Что такое задержка распространения в проектировании высокоскоростных печатных плат?

В проектировании высокоскоростных устройств вы можете столкнуться с вопросом о том, что такое задержка распространения. Altium Designer предоставляет вам инструменты проектирования, чтобы профессионально работать с этим.

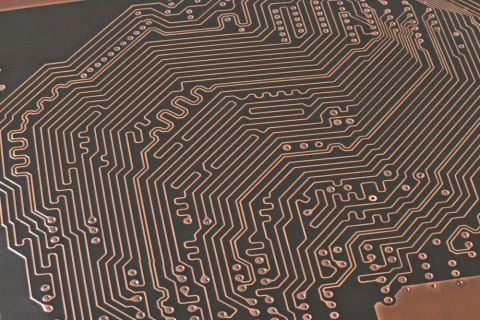

Каждый электромагнитный сигнал, будь то цифровой сигнал, передаваемый по печатной плате, или волна, распространяющаяся через воздух между антеннами, будет иметь конечную скорость. Эта конечная скорость является временем распространения сигнала. Это важная величина по нескольким причинам, которые в основном находят применение в дизайне печатных плат высокой скорости и в проектировании РЧ систем. Дифференциальные цифровые интерфейсы и фазочувствительные РЧ-дизайны являются наиболее важными областями, где время распространения играет важную роль и становится важным параметром в компоновке печатной платы.

В этой статье я объясню, где именно время распространения используется в некоторых базовых расчетах для дизайна печатных плат. Мы скоро увидим, что важное применение времени распространения возникает, когда нам нужно обеспечить согласованный фазовый отклик через несколько соединений на печатной плате.

Что такое время распространения?

Задержка распространения относится к обратной величине скорости распространения электромагнитного сигнала. Этот термин в основном используется в индустрии печатных плат (PCB) для обозначения скорости сигнала, в то время как разработчики интегральных схем используют тот же термин для обозначения времени, необходимого для переключения логического состояния с входа на выход. В PCB задержка распространения сигнала выражается в единицах времени на расстояние (обратная величина скорости). Другими словами, если вы знаете скорость света для сигнала в PCB, инвертируйте значение, и вы получите задержку распространения.

Когда разработчик PCB планирует дизайн линии передачи для интерфейса с контролируемым импедансом, ему может потребоваться рассчитать задержку распространения для сигнала на этой линии. Факторы, определяющие задержку распространения сигнала, включают:

- Диэлектрическую проницаемость субстрата

- Значение импеданса (на самом деле геометрию линии передачи)

- Расстояние до плоскости(ей) отсчета линии передачи

- Для дифференциальной пары, расстояние до другого проводника в паре

- Эффекты волоконной текстуры в диэлектрическом материале PCB

Определение для Стриплайнов и Микрополосковых линий

Самое простое определение можно получить, рассматривая скорость света в вакууме; используя значение Dk материала вашей печатной платы, вы можете определить скорость сигнала:

Инвертируйте это значение, и вы получите задержку распространения в единицах времени на расстояние. Типичное значение для 50 Ом микрополоски составляет ~150 пс/дюйм, а для стриплайнов типичное значение составляет ~171 пс/дюйм; оба предполагают диэлектрики Dk = 4. Почему микрополоска должна иметь другую задержку распространения по сравнению со стриплайном? Это из-за зависимости от геометрии соединения. Для стриплайна маршрутизация находится на поверхностном слое, и некоторые линии электрического поля будут проходить через воздух, поэтому скорость сигнала определяется с использованием "эффективного" значения Dk:

Далее, нам нужна формула для эффективного значения Dk для микрополосковых линий. Это значение зависит от геометрии линии передачи и может быть рассчитано из уравнений Максвелла. Используя квази-ТЕМ теорию для линий передачи, было показано, что задержка распространения сигнала на микрополоске следующая:

Здесь, ш и в являются шириной микрополоскового проводника и расстоянием до земляного слоя соответственно. Эта формула может использоваться вручную и известно, что она точна в диапазоне целевых значений импеданса в пределах квази-ТЕМ лимита.

Определение из теории линий передачи

В более общем смысле, существует определение для задержки распространения, которое можно найти непосредственно из теории линий передачи. Эта формула для задержки распространения требует от вас знания значений распределенных элементов цепи для вашей конкретной линии передачи:

Если инвертировать это уравнение, вы получите задержку распространения.

Это уравнение универсально верно как квази-ТЕМ модель, но его не так просто использовать для проектирования. Вместо этого, оно обычно используется как часть регрессионной модели, где значения распределенных элементов в формуле определяются через процесс извлечения из измерений параметров сети в эксперименте или симуляции. Процессы и алгоритмы, используемые для извлечения модели цепи, являются темами для другой статьи.

Где используется задержка распространения

В общем, вам не нужно знать или рассчитывать задержку распространения для каждого отдельного сигнала или соединения на вашей печатной плате.

Тайминг в дизайне высокоскоростных печатных плат

Высокоскоростные сигналы, будь то интерфейсы с синхронизацией по источнику, параллельные шины или последовательные дифференциальные пары, должны поступать на приемник в пределах определенного временного запаса. В общем случае, когда время нарастания сигналов быстрее, временной запас будет меньше. Это означает, что для применения настройки длины, которая обеспечивает прибытие сигналов в пределах требуемого временного запаса, необходимо знать постоянную распространения.

Основное временное ограничение, определяющее работоспособность высокоскоростного интерфейса, - это разница во времени между двумя сигналами, которую мы будем называть Δt. Связь между допустимым несоответствием длины и допустимым временным несоответствием задается следующим образом:

Это несоответствие длины/времени возникает в трех важных случаях:

- Между сигналами в параллельной шине (например, DDR)

- Между двумя дорожками в дифференциальной паре

- Между несколькими дифференциальными парами

В качестве примера применения настройки длины в реальной ситуации, мне хотелось бы показать изображение ниже интерфейса CSI-2 на FPGA с его маршрутизацией ухода. На изображении ниже показаны пять дифференциальных пар (4 сигнальных линии и одна линия часов), которые составляют интерфейс CSI-2, который обычно маршрутизируется в разъем камеры. Мы можем видеть один участок настройки длины, примененный в дифференциальной сети AWR_3_CSI2_TX0, который обеспечивает минимизацию разницы во времени между этими двумя дорожками. Поскольку программное обеспечение для проектирования знает допустимое отклонение во времени (оно выбирается конструктором) и задержку распространения (она устанавливается в правилах проектирования), инструмент компоновки печатной платы может проверить наличие разницы в длине, автоматически применяя вышеуказанную формулу.

Лучшее программное обеспечение для проектирования печатных плат автоматически пересчитывает разрешенное несоответствие времени и фактическое несоответствие длины между двумя сигналами, но только в том случае, если одно из этих ограничений определено в правилах вашего проекта и известна задержка распространения. Если ваше программное обеспечение для проектирования может выполнить расчет импеданса для ваших несоответствующих сетей, то оно также может определить задержку распространения для этой конкретной геометрии линии передачи, и вам не придется вычислять это вручную.

Определение входного импеданса

Еще одна важная область, где требуется расчет задержки распространения, как в радиочастотном, так и в цифровом проектировании, это определение входного импеданса. Это используется для определения:

- Будет ли сигнал отражаться на входе соединения; это используется для определения коэффициента отражения на входе (значение S11);

- является ли разрыв импеданса физически достаточно большим, чтобы создать заметное отражение в широкополосных (цифровых) сигналах.

В первом случае мы хотим определить, сможет ли сеть согласования импеданса (шлейф или дискретные элементы) обеспечить желаемый целевой входной импеданс. В последнем случае мы хотим узнать, на каких частотах сигнал начнет сильно отражаться от разрыва импеданса. Формула для определения входного импеданса между источником и нагрузкой, соединенными с линией передачи, приведена на изображении ниже:

Исходя из этого, вы можете делать такие вещи, как предсказывать точные частоты, на которых нагрузка и источник будут идеально согласованы по импедансу с линией передачи длиной l и с характеристическим импедансом Z0.

Фазовая характеристика в РЧ-дизайне

Наконец, другой распространенный случай, когда необходимо знать задержку распространения, это фазовая характеристика РЧ-цепей. В некоторых РЧ-проектах требуется инженерная настройка фазовой характеристики сигнала, подаваемого на межсоединение. Фазовая характеристика также связана с задержкой распространения следующим образом:

Другими словами, когда сигнал с известной частотой и временем распространения проходит расстояние L по соединению, мы можем рассчитать его фазовый сдвиг. Этот фазовый отклик используется в таких областях, как печатное проектирование РЧ-схем, для учета любых эффектов, требующих вмешательства, таких как резонаторы и фильтры. Например, если вам нужно измерить фазу входящего сигнала относительно какого-либо эталона, вам необходимо знать фазовый сдвиг сигнала вдоль вашего соединения, что требует знания времени распространения в системе.

Самая важная область, где применяется согласование фазового отклика в проектировании РЧ-печатных плат, - это фазированные антенные решетки. Эти антенны специально используются в радарах высокого разрешения, беспроводных системах MIMO и уникальных датчиках миллиметрового диапазона. Эти системы требуют фазового согласования между множеством элементов антенны, и каждый элемент антенны будет иметь линию подачи, соединяющую его с чипом передатчика. Фазовое согласование необходимо для направления лучей к целям или пользователям мобильных устройств, и правильный способ обеспечения фазового согласования по всей решетке - это реализация настройки длины, аналогично тому, что вы делали бы в большой параллельной шине однополярных сигналов.

Простой пример антенной решетки с последовательным питанием 4x серии (плюс 2 заглушки антенны) показан ниже. Современные автомобильные радары имеют гораздо больше антенн, с виртуальными размерами решеток, достигающими сотен антенн.

В этих системах рабочая частота обычно находится в диапазоне миллиметровых волн (на уровне WiFi или выше), поэтому линии передачи обычно прокладываются как копланарные волноводы. Уравнения для расчета копланарных волноводов сильно отличаются от стандартных микрополосков, поэтому для определения задержки распространения этих линий может потребоваться решатель электромагнитных полей.

Всякий раз, когда вам нужно спроектировать печатную плату, учитывающую задержку распространения, убедитесь, что вы используете полный набор функций проектирования печатных плат и мирового класса инструменты CAD в Altium Designer. Для реализации сотрудничества в современной междисциплинарной среде, инновационные компании используют платформу Altium 365 для легкого обмена данными проектирования и запуска проектов в производство.

Мы только коснулись поверхности возможностей Altium Designer на Altium 365. Начните вашу бесплатную пробную версию Altium Designer + Altium 365 сегодня.