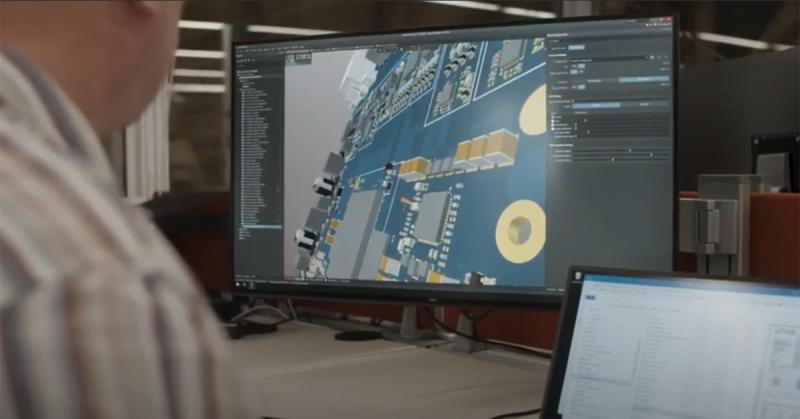

Altium Designer - 回路・基板設計ソフトウェア

簡単、効果的、最新: Altium Designerは、世界中の設計者に支持されている回路・基板設計ソフトウェアです。 Altium DesignerがどのようにPCB設計業界に革命をもたらし、設計者がアイデアから実際の製品を作り上げているか、リソースで詳細をご覧ください。

On-Demand Webinars

Explore upcoming and on-demand webinars for Altium Designer.

ビデオ

Watch videos for Altium Designer to learn more!

Customer Success Stories

Discover customers finding success with Altium Designer!

Articles

Explore more popular content for Altium Designer!