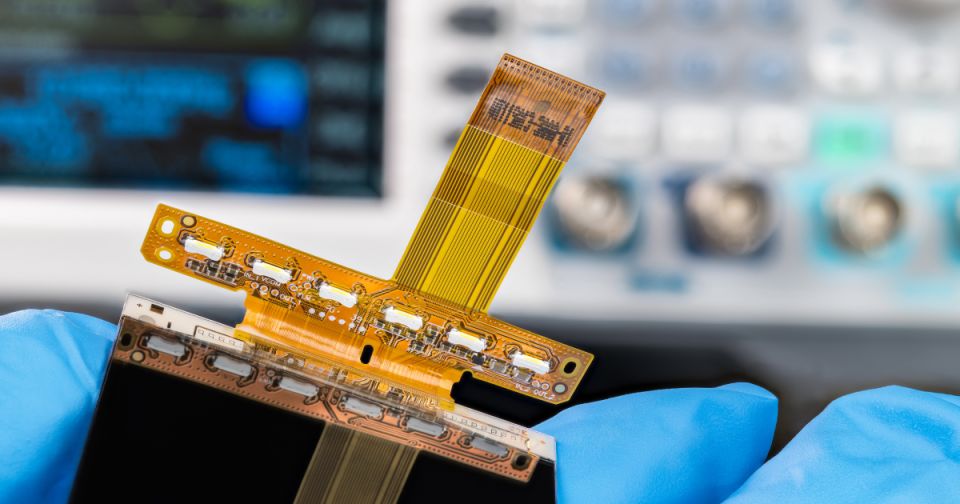

PCBレイアウト

高品質なPCBレイアウトでは、高密度な配線、低EMI、機械的制約を考慮した部品配置を行います。Altium DesignerでのPCBレイアウトの方法やヒントをライブラリのリソースでご覧ください。

ビデオ

Watch videos for PCB layout to learn more!

Customer Success Stories

Discover customers finding success with Altium's PCB Layout solutions!

Articles

Explore more popular content for PCB layout!