¿Qué es el estándar JESD204C para ADCs/DACs?

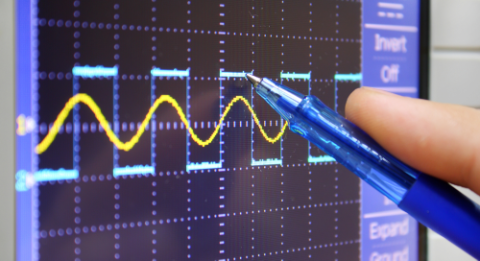

JESD204C proporciona una interfaz estandarizada para ADCs de RF con alta tasa de muestreo, que ahora están apareciendo más en aplicaciones espaciales comerciales.

Las interfaces seriales han tenido dificultades para mantener el ritmo con las necesidades de los componentes de conversores de datos de alta tasa de muestreo, a saber, ADCs y DACs. Una opción para hacer esto anteriormente eran los enlaces LVDS entre los conversores de datos y un controlador anfitrión. Estos enlaces proporcionarían altas tasas de datos a través de pares diferenciales a un solo dispositivo, ofreciendo una transferencia de datos de alta capacidad desde ADCs de muestreo rápido. Más tarde, JEDEC lanzó la especificación JESD204, y desde entonces ha sido incorporada en muchos componentes como una interfaz de conversor de datos.

La iteración más reciente de los estándares de interfaz JESD204, actualmente JESD204C, trae tasas de datos extremas a componentes ADC/DAC rápidos que se utilizan para muestrear señales a tasas de muestreo muy altas. Ahora que la iteración más nueva del estándar ha estado disponible por poco más de 2 años, hay muchos componentes disponibles que pueden usarse con FPGAs para proporcionar muestreo ultra rápido, transmisión y DSP en sistemas RF.

Resumen de JESD204C

El estándar JESD204C es la iteración más reciente del estándar general JESD204, el cual es publicado y mantenido por JEDEC. El estándar fue desarrollado para reemplazar el uso de enlaces LVDS entre convertidores de datos y sus sistemas anfitriones. Define una interfaz y protocolo seriales utilizados en ADCs/DACs de alta tasa de muestreo para el muestreo de señales, síntesis y sincronización. El aspecto de sincronización es importante para esta interfaz ya que permite a un único controlador anfitrión sincronizar el muestreo de señales y la síntesis a través de múltiples dispositivos.

Algunos de los parámetros operativos primarios implementados en la capa física se listan en la tabla a continuación. La iteración actual JESD204C mejora en la tasa de datos y las características de codificación de la iteración previa JESD204B, la cual utilizaba codificación 8b/10b con una tasa de datos máxima de 12.5 Gbps. Esta interfaz se puede encontrar en ADCs/DACs que operan desde 100 MSps hasta 1 GSps o más.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Ejemplo de Topología

La topología de una interfaz JESD204C depende de la Subclase de la interfaz. JESD204B introdujo las Subclases 1 y 2 para implementar una estrategia de sincronización conocida como latencia determinística. Esta estrategia logra la sincronización entre dispositivos determinando el desfase entre los flujos de datos que se transmiten al controlador principal.

- Subclase 0 - Sin soporte de latencia determinística (compatible con JESD204A)

- Subclase 1 - Latencia determinística lograda usando un oscilador de referencia externo (SYSREF) como señal de tiempoSubclase 2 - Latencia determinística lograda usando un pin SYNC entre el controlador principal y el ADC/DAC

Se muestran dos implementaciones de la interfaz en el gráfico a continuación.

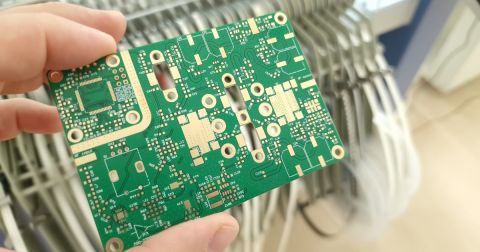

DATA1 y DATA2 se enrutan como pares diferenciales; cada carril en estos grupos de E/S es un par diferencial y un dispositivo dado podría tener múltiples carriles (algunos productos tienen hasta 8 por dispositivo). En ambas Subclases, la fuente de reloj se enruta a todos los dispositivos de manera sincrónica con la fuente. El tiempo y la latencia determinística se logran en cada Subclase mediante la coincidencia adecuada de SYSREF y DCLK/SYNC con los tiempos de establecimiento y mantenimiento, así como entre sí cuando se distribuyen a través de múltiples conversores de datos.

Enrutamiento, Compensación de Retardo y Latencia

Se mencionó anteriormente la latencia determinística: esta es la técnica mediante la cual un único controlador anfitrión puede sincronizar la recolección y síntesis de datos a través de múltiples dispositivos con un tiempo preciso de tal manera que el desfase temporal entre los marcos de muestreo es conocido. Esto se corrige mediante la afinación de los retrasos de las trazas entre sí para que los retrasos entre ellos coincidan. Una interfaz JESD204B o JESD204C utiliza la coincidencia de retrasos en los bits de control que provienen de SYSREF (en la Subclase 1) o de los pines SYNC (en la Subclase 2).

La tabla a continuación describe los requisitos de coincidencia de longitud/retraso en las señales de temporización para cada Subclase en las interfaces JESD204B y JESD204C.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

La principal diferencia aquí es cómo se tratan las redes SYNC. En la Subclase 1, estas redes solo se utilizan para la sincronización de grupos de códigos, mientras que también se utilizan para el temporizado en la Subclase 2. Por lo tanto, JESD204C tiene menos señales para un número dado de canales de E/S en los convertidores de datos.

¿Por qué JESD204C en lugar de LVDS?

La ventaja de la interfaz JESD204C para el muestreo y la síntesis de alta velocidad en frecuencias de GHz es esta capacidad para eliminar el desfase y la discrepancia de latencia entre múltiples conversores. Existe un presupuesto de desfase para cualquier interfaz JESD204, que es la cantidad máxima de desfase que se puede compensar en el esquema de temporización del sistema para garantizar una latencia determinística dentro de los límites del ruido de fase. El objetivo es asegurar que el controlador anfitrión conozca las discrepancias de fase de los flujos de datos entrantes resultantes y pueda compensarlas en lógica, estableciendo así el verdadero temporizado entre las señales muestreadas.

La otra razón para el uso de JESD204C es que reduce los requisitos de enrutamiento y temporización en el diseño del PCB. En una implementación típica, los pares diferenciales DATA1 y DATA2 provenientes del Dispositivo 1 y Dispositivo 2 tendrán algún desfase entre ellos. Con LVDS, esto requeriría emparejar pares diferenciales que corran en paralelo entre sí. En JESD204C, solo necesitamos eliminar el desfase a través de las redes DCLK y SYSREF/SYNC, pero no las redes de datos entre dispositivos. Esto hace que la interfaz sea esencial en dispositivos de señal mixta de alta densidad.

Los diseñadores que construyen tecnologías avanzadas para la industria aeroespacial pueden implementar el estándar JESD204C utilizando las mejores herramientas de diseño de productos de la industria en Altium Designer®. Cuando hayas terminado tu diseño y quieras enviar los archivos a tu fabricante, la plataforma Altium 365™ facilita la colaboración y el compartir tus proyectos.

Solo hemos arañado la superficie de lo que es posible con Altium Designer en Altium 365. Comienza tu prueba gratuita de Altium Designer + Altium 365 hoy.