ADC/DAC用のJESD204C規格とは何ですか?

シリアルインターフェースは、高サンプルレートのデータコンバータコンポーネント、特にADCとDACのニーズに追いつくのが難しいとされてきました。これを実現する一つの方法は、以前はデータコンバータとホストコントローラー間のLVDSリンクでした。これらのリンクは、高速サンプリングADCからの高スループットデータ転送を提供するために、差動ペアを介して単一デバイスに高データレートを提供します。後に、JEDECはJESD204仕様を発表し、それ以来多くのコンポーネントにデータコンバータインターフェースとして組み込まれています。

JESD204インターフェース標準の最新の反復である現在のJESD204Cは、非常に高いサンプルレートで信号をサンプリングするために使用される高速ADC/DACコンポーネントに極端なデータレートをもたらします。この標準の最新の反復が2年以上前に登場して以来、超高速サンプリング、伝送、およびRFシステムでのDSPを提供するためにFPGAと共に使用できる多くのコンポーネントが利用可能になりました。

JESD204Cの概要

JESD204C規格は、JEDECによって公開および維持されている一般的なJESD204規格の最新の反復です。この規格は、データコンバータとそのシステムホスト間のLVDSリンクの使用を置き換えるために開発されました。高サンプルレートのADC/DACでの信号サンプリング、合成、および同期に使用されるシリアルインターフェースとプロトコルを定義しています。このインターフェースにおいて重要なのは同期の側面で、これにより単一のホストコントローラーが複数のデバイスにわたって信号サンプリングと合成を同期させることができます。

物理層で実装されている主要な動作パラメーターのいくつかは、以下の表にリストされています。現在のJESD204C反復は、最大データレートが12.5 Gbpsで8b/10bエンコーディングを使用していた前のJESD204B反復のデータレートとエンコーディング特性を改善しています。このインターフェースは、100 MSpsから1 GSps以上で動作するADC/DACに見られます。

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

例示トポロジー

JESD204Cインターフェースのトポロジーは、インターフェースのサブクラスに依存します。JESD204Bは、決定論的レイテンシとして知られる同期戦略を実装するために、サブクラス1と2を導入しました。この戦略は、ホストコントローラーに送信されるデータストリーム間の位相ミスマッチを決定することにより、デバイス間で同期を達成します。

- サブクラス0 - 決定論的レイテンシのサポートなし(JESD204Aとの後方互換性あり)

- サブクラス1 - 外部リファレンスオシレータ(SYSREF)をタイミング信号として使用して決定論的レイテンシを達成

- サブクラス2 - ホストコントローラーとADC/DAC間のSYNCピンを使用して決定論的レイテンシを達成

以下のグラフィックに示されているように、インターフェースの2つの実装があります。

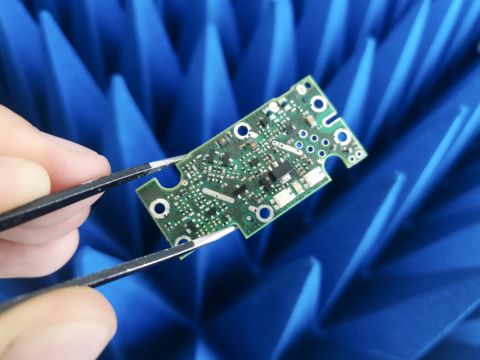

DATA1とDATA2は差動ペアとして配線されており、これらのI/Oグループ内の各レーンは差動ペアであり、特定のデバイスには複数のレーンが存在する場合があります(一部の製品ではデバイスごとに最大8つまであります)。両サブクラスにおいて、クロックソースはソース同期方式で全デバイスにルーティングされます。各サブクラスにおいて、タイミングと決定論的レイテンシは、SYSREFとDCLK/SYNCをセットアップ・ホールド時間に適切にマッチングさせること、および複数のデータコンバーターにわたって分配される際に互いにマッチングさせることによって達成されます。

ルーティング、デスキュー、およびレイテンシ

上記で述べた決定論的レイテンシは、単一のホストコントローラーが複数のデバイスにわたってデータ収集と合成を正確なタイミングで同期させる技術であり、サンプリングフレーム間のタイミングスキューが既知であることを意味します。これは、トレース遅延の調整によって修正され、それらの間の遅延が一致するようにします。JESD204BまたはJESD204Cインターフェースは、SYSREF(サブクラス1内)またはSYNCピン(サブクラス2内)から供給される制御ビット内で遅延マッチングを使用します。

以下の表は、JESD204BおよびJESD204Cインターフェースの各サブクラスにおけるタイミング信号の長さ/遅延マッチング要件を概説しています。

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ここでの主な違いは、SYNCネットの扱い方です。サブクラス1では、これらのネットはコードグループの同期のためにのみ使用されますが、サブクラス2ではタイミングにも使用されます。したがって、JESD204Cは、データコンバータのI/Oチャネルの数に対して、より少ない信号を持っています。

JESD204CとLVDSの比較理由は何ですか?

JESD204Cインターフェースの利点は、GHz周波数での高速サンプリングと合成において、複数のコンバーター間でのスキューとレイテンシの不一致を排除できる能力にあります。任意のJESD204インターフェースにはいくらかのスキューバジェットがあり、これはシステムタイミングスキーム内で補償できる最大のスキュー量であり、位相ノイズの限界内で決定論的なレイテンシを保証するために必要です。目標は、ホストコントローラーが結果として得られる入力データストリームの位相の不一致を知り、ロジックでそれを補償できるようにし、サンプリングされた信号間の真のタイミングを確立することです。

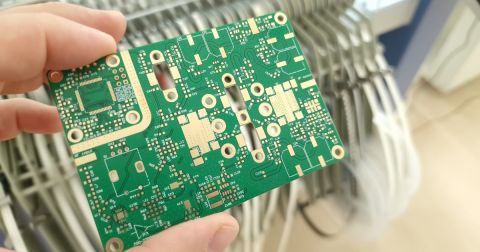

JESD204Cを使用するもう一つの理由は、PCBレイアウトにおけるルーティングとタイミング要件を減らすことができる点です。典型的な実装では、デバイス1とデバイス2から来るDATA1とDATA2の差動ペアには、それらの間にいくらかのスキューが存在します。LVDSでは、これは互いに平行に走るマッチング差動ペアを必要とします。JESD204Cでは、DCLKとSYSREF/SYNCネット間のスキューのみを排除すればよく、デバイス間のデータネットでは不要です。これにより、インターフェースは高密度混合信号デバイスにとって不可欠なものとなります。

航空宇宙用の先進技術を構築する設計者は、業界最高の製品設計ツールを使用してJESD204C標準を実装できます。Altium Designer®。設計が完成し、製造業者にファイルをリリースしたい場合、Altium 365™プラットフォームを使用すると、プロジェクトの共有やコラボレーションが簡単になります。

Altium DesignerとAltium 365で可能なことの表面をかすめただけです。今すぐAltium Designer + Altium 365の無料トライアルを始めましょう。