エレクトロニクス向け統合設計環境とは?

機械的な制約の発見が遅れることは、エレクトロニクス開発プロジェクトでスケジュール遅延や手戻りを招く一般的な原因です。

典型的な例を考えてみましょう。設計開始から3か月が経過し、回路図は完成、PCBレイアウトもほぼ完了しています。ところがその段階になって初めて、メイン基板の数ミリ上に2枚目のPCBが取り付けられる予定だと顧客から伝えられます。顧客としては、以前共有した写真を見れば明らかだと思っていたのです。この時点では、すでに選定済みのコネクタや部品の高さが高すぎることが判明し、電圧・電流要件のために調達が難しい部品を再選定せざるを得なくなります。正式に要件として取り込まれていなかった制約に対応するために、数週間分の作業が失われます。

この種の問題は珍しくありません。むしろ、分断された設計ワークフローがもたらす当然の帰結です。

重要なポイント

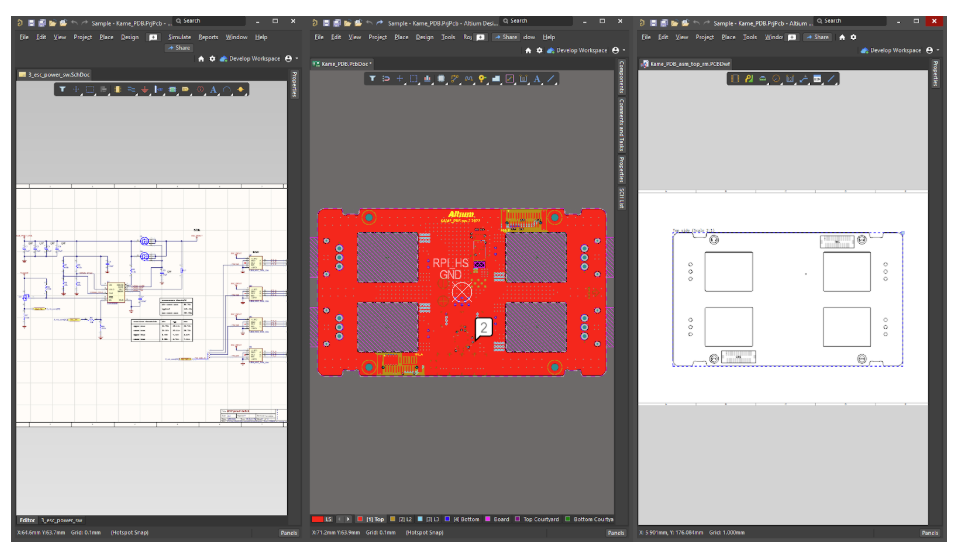

- 統合設計環境では、回路図作成、PCBレイアウト、シミュレーション、MCAD連携、データ管理が一体化されており、エンジニアは分断されたツール間を行き来する必要がありません。

- 設計ルールや制約条件(クリアランス、間隔、部品高さなど)は、製造用データをリリースした後ではなく、設計中にリアルタイムでチェックされなければなりません。

- 機械およびファームウェアの制約は、プロジェクトの開始時点で導入する必要があります。部品選定後にそれらが判明すると、不必要な手戻りや遅延につながります。

問題点:1枚の基板を作るのに6つのツール

多くのハードウェアチームでは、設計ワークフローが複数の分断されたツールにまたがっています。パッドスタック定義はあるアプリケーションにあり、回路図シンボルやライブラリは別のツールで管理され、しかもローカルまたはネットワーク上の異なるフォルダに保存されていることが少なくありません。PCBレイアウトはさらに別の場所で行われます。システム統合、シグナルインテグリティ、EMI解析は通常、追加の専用アプリケーションで実施されます。プロジェクト管理やタスク管理はWebベースであることが多く、エンジニアがオフラインで作業しているとアクセスできない場合もあります。

その結果、エンジニアは回路図作成から製造可能なPCBに至るまでの設計を進めるだけでも、少なくとも5種類の異なるツールを習得し、使いこなし続けなければなりません。

小規模チームでは、この分断がさらに余計な負荷を生みます。ツール間の移動には頻繁なファイルのエクスポートとインポートが必要で、各段階で変換エラーのリスクが伴います。ライブラリやフットプリントは使用可能な状態を保つために特定のディレクトリ構成に配置しなければならず、ファイルの置き場所を誤ると、部品が回路図からレイアウトへ正しく受け渡されなくなることがあります。

回路図シンボル、PCBフットプリント、正しいファイルバージョンを探すだけで多くの時間が失われます。本来なら些細な作業であるはずなのに、プロジェクト全体では何日、時には何週間も費やされることがあります。

これだけ多くのツールを使っていても、最終的な調整は依然としてメールやスプレッドシート頼みです。ツール同士はほとんど連携しておらず、設計プロセス全体を通じた共有可視性はほとんど得られません。

統合設計環境が実際に意味するもの

エレクトロニクス向けの統合設計環境とは、単一のアプリケーション、または緊密に連携したツール群によって、ハードウェア設計ワークフロー全体を支援するものです。

- 回路設計のための回路図作成

- 部品配置と配線のためのPCBレイアウト

- 製造前検証のためのシミュレーション

- 電気チームと機械チームが同じデータを基に作業できるECAD-MCAD連携

- 部品ライブラリ、プロジェクトファイル、設計要件のためのデータ管理

統合環境では、設計のすべての段階で同じ基盤データが使われます。回路図で行った変更はPCBレイアウトに直接反映されます。基板外形や筐体クリアランスといった機械的制約も、更新されるたびに電気設計環境から確認できます。

これにより、分断されたアプリケーションをつなぎ合わせたツールチェーンでよく発生する、手動エクスポート、ファイルインポート、バージョン不一致がなくなります。

- 電気チームと機械チームの間でこれが実際にどのように機能するかについて詳しくは、Altium Develop のECAD-MCAD collaborationをご覧ください。

統合がフィードバックループを閉じる仕組み

これはパワーエレクトロニクスのプロジェクトでよくある状況です。PCBレイアウトはあるツールで作成され、回路図作成は別のツールで行われ、筐体設計は機械エンジニアがPTC Creoで別途進めています。これらの環境はどれもライブな設計データを共有していません。

このケースでは、筐体はPCBをぎりぎり収められる程度で、ケーブルアセンブリは必要な間隔要件に違反していました。これらは個別に見れば設計ミスではありません。問題が起きたのは、機械と電気の全体文脈を一つの環境で可視化できなかったためです。競合を解消するには、電気チームと機械チームの間で何度もやり取りを繰り返す必要があり、スケジュールに2〜3週間の遅れが追加されました。

ECADツールとMCADツールが統合されていれば、このフィードバックループは閉じられます。機械エンジニアは筐体モデルから基板外形と制約を直接定義でき、それらの制約はPCBレイアウトに反映されます。電気エンジニアは、部品選定や配線方針を確定する前に、利用可能な基板面積、検証済みの取付穴位置、部品高さ制限を即座に確認できます。

この双方向同期により、反復回数が減り、後工程での競合を防ぎ、設計サイクル全体を短縮できます。

- ECAD-MCAD連携の詳細については、MCAD CoDesigner documentationをご覧ください。

リアルタイム設計ルール検証が基板を救う

リターンパスビア、クリアランス違反、製造性設計(DFM)や組立性設計(DFA)に関する間隔エラーは、PCBの手戻りや再試作の一般的な原因です。こうした問題は、設計ルールをレイアウト完了後にしかチェックしない場合によく見逃されます。

リアルタイム設計ルール検証では、違反が発生した瞬間にそれを検出します。クリアランス制約に違反すれば、即座に可視化されます。配線幅が割り当てられたネットクラスの要件を満たしていなければ、そのエラーはレイアウト上で直接強調表示されます。

このアプローチは、設計作業が完了してから問題を洗い出すバッチ型の設計ルールチェックとは異なります。バッチチェックでは、数時間前あるいは数日前に入り込んだ問題が後になって見つかります。リアルタイムチェックは、レイアウト中に制約を適用することで、こうしたエラーが広がるのを防ぎます。

「問題なく動いている」の本当のコスト

「今のツールチェーンでも問題なく動いている」という言葉は、しばしばそのプロセスが脆弱であることを意味します。

あるプロジェクトでは、ケーブルおよびハーネス設計に回路図作成ソフトウェアが使われていました。技術的には可能でしたが、その用途向けに設計されたツールではありませんでした。その結果、電気的変更が図面に自動反映されず、すべてのラベルやテキストフィールドを手作業で更新しなければなりませんでした。

これにより、予想どおりの不具合が発生しました。実際の設計とドキュメントが同期していなかったため、複数のケーブルアセンブリが誤配線のまま製作されました。エンジニアは、本来ツール自体が防ぐべきだったエラーの確認、再確認、修正に多くの時間を費やしました。手動更新と検証の継続的な負荷により、個人の生産性は推定で40〜50%まで低下しました。

システムは機能していましたが、それは単に即座に破綻しなかったという意味にすぎません。「問題ない」の本当の代償は、手戻り、遅延、そしてエンジニアリング能力の低下として支払われていたのです。

ファームウェアと機械要件が後から現れるとき

最近のあるプロジェクトでは、メインPCBの設計が完了し、部品表も確定し、製造リリース直前の状態になっていました。

その時点で、新たな制約が浮上しました。補助LED基板がメイン基板の上に取り付けられ、垂直方向のクリアランスはわずか10 mmしかないというのです。

この遅れて出てきた要件により、影響範囲の再設計が必要になりました。既存のコネクタは許容高さを超えていました。十分な電流容量を持つ部品は、低背パッケージでは入手できませんでした。高さ要件を満たす代替部品は、最小発注数量が現実的でないか、すでに廃止品でした。

代替案の評価に約4週間を費やし、追加のコンサルティング費用として2,000ドル(プロジェクト総予算のおよそ10%)が発生しましたが、最終的に分かったのは当初の設計アプローチが成立しないということだけでした。

さらに問題を悪化させたのが、中国の旧正月による操業停止で、製造が遅延したことです。本来であれば10月または11月に出荷されるはずだった基板は、3月まで納品されませんでした。

根本原因は技術的な失敗ではなく、プロセス上の失敗でした。機械的制約がプロジェクト開始時に共有されておらず、電気・機械・ファームウェアの各チームが設計サイクルの早い段階でシステムレベル要件を確認・検証できる共有環境も存在しなかったのです。

なぜすべてが連携して動く必要があるのか

ソフトウェアシステムは、部分的な障害に耐えられることがよくあります。1つの機能が壊れても、アプリケーションの他の部分は動き続けるため、問題を段階的に修正できます。

ハードウェアシステムはそうはいきません。

電源アーキテクチャが誤っていたり、レベルシフタの適用を誤っていたり、基本的なインターフェースが成立していなかったりすると、基板の大部分が動作しないか、システム自体がまったく起動しない可能性があります。ハードウェアでは、有意義な試験を始める前に、すべてのサブシステムにわたって高いレベルの正しさが求められます。

ハードウェアが本質的に統合された存在である以上、開発プロセスもまた統合されていなければなりません。要件をメールスレッドの中に埋もれさせてはいけません。設計ルールをレイアウト工程の最後にしか確認しないようではいけません。機械的制約を開発開始から数か月後に初めて知るようでは、手戻りと遅延は避けられません。

設計ツールはこの現実を反映すべきです。電気、機械、部品データは、設計サイクル全体を通じて接続され、可視化され、アクセス可能でなければならず、分断されたファイルや受け渡しで管理されるべきではありません。

分断されたツールチェーンから脱却したいチームにとって、Altium Develop は良い出発点です。

信頼性の高いパワーエレクトロニクスでも、高度なデジタルシステムでも、Altium Develop はあらゆる専門分野を1つの協働する力へと結び付けます。サイロ化からの解放。制約からの解放。エンジニア、設計者、イノベーターが一体となり、制約なく共創する場所です。今すぐ Altium Develop を体験してください。

よくある質問

エレクトロニクス向けの統合設計環境とは何ですか?

統合設計環境は、回路図作成、PCBレイアウト、シミュレーション、ECAD-MCAD連携、データ管理を、単一の接続されたワークフローにまとめるものです。エンジニアは別々のツール間でファイルを受け渡す代わりに、共有データを基に作業するため、変更が設計の各段階に自動的に反映されます。

統合環境はどのようにして手戻りやスケジュール遅延を減らすのですか?

電気、機械、製造に関する制約をリアルタイムで検証することで、クリアランス違反、部品高さ制限、配線競合といった問題を、数週間後ではなく発生したその場で検出できます。これにより、通常は納期遅延やコスト増加の原因となる後工程での再設計を防げます。

なぜECAD-MCAD統合はプロジェクト初期に重要なのですか?

筐体形状、基板のスタッキング、コネクタの位置合わせといった機械的制約は、部品選定やレイアウトの判断に直接影響します。こうした制約を設計初期から可視化しておけば、後になって実現不可能だと判明する部品やアーキテクチャを選んでしまうことを防げます。

リアルタイムの設計ルールチェックは、従来のバッチチェックと何が違うのでしょうか?

リアルタイムチェックでは、ルール違反が発生した瞬間にエラーが通知されるため、問題が波及する前にエンジニアが修正できます。一方、バッチチェックではレイアウト完了後にしか問題を特定できないため、多くの場合、大幅な手戻りや再作業が必要になります。