Everything You Need to Know About Microvias in Printed Circuit Design

Have you ever wondered how designers pack so much functionality into such a small space? You can thank HDI design techniques and microvias in printed circuit design. These small structures let traces reach inner layers of a PCB with high interconnect density and high layer count. These structures have been around for years, but they are becoming more common in a variety of systems that require multiple functions on a single circuit board. If you've done a size study and you've determined you'll need 6 mil or smaller traces to fit all your components in your printed circuit board, your design is likely dense enough that microvias are needed to support routing between layers. Here's how these structures are formed and what you need to know about PCB microvias.

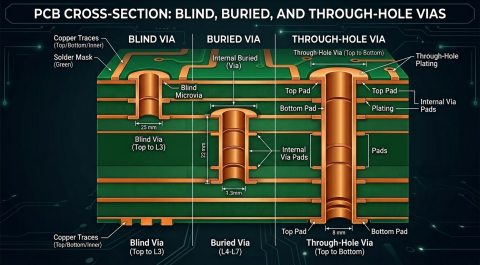

As it's name suggests, a microvia is just a very small version of a typical via, but the structure is a bit different. Microvias have conical frustum shape; the via slopes inwards as it makes a layer transition and terminates at a pad in the next layer. Ideally, microvias will only span a single layer for maximum reliability. Designers can use stacked microvias to form connections across multiple layers, where blind and buried microvias are built up into a stack to reach across multiple layers. These stacked via designs are known to have reliability problems, so staggered versions are often preferred. There has been some debate about this point, which I'll outline below.

Microvias in Your ECAD Software

Defining microvias starts in the PCB stackup editor, where layer pairs are defined and materials are selected. Note that you need to choose an appropriate laminate that can support the fabrication process you want to use. After building a proposed stackup, I always advise sending it to your fabricator for a review and getting their input as to manufacturability with microvias.

Once you're in the PCB editor, pay attention to the layer pair designation on the pad in the PCB layout. An example from an mmWave RF board with 6 mil vias is shown below. Three through-hole vias are shown in this image for comparison. The 6 mil number is important as this is right at the upper limit of what the IPC considers microvias.

Taking the dielectric layer thickness and the hole diameter together gives the aspect ratio of microvias placed in the PCB layout. Care should be taken when sizing these structures as the aspect ratio is also related to reliability.

Fabrication

Exactly how small are microvias? If you ask most designers, they might tell you that they would consider a microvia to be a via with a diameter less than about 150 µm (6 mils). Depending on the size of the vias, they can be mechanically drilled and plated (followed by stacking and pressing each layer), or they can be formed with a high-power laser. The latter process is constantly being improved and is preferred in high volume PCB manufacturing thanks to its high throughput. New advances in laser drilling techniques are pushing microvia sizes down to as small as 15 µm.

After drilling and cleaning, the via hole is plated, either with a sputtering process, electrolytic deposition, or electroless copper plating process. The goal in the plating process is to prevent the formation of voids, dimples, bumps, or any other structural defect in the filled via. Voids are also a reliability concern as stress can concentrate around the edge of the void where copper is thinner if stress is applied to the via structure.

During fabrication, laser-drilled microvias have a lower potential for manufacturing defects than normal vias. Mechanically-drilled microvias can have defects due to drill vibration as the drill wears out, and mechanical microvia drilling is only useful down to 6 to 8 mil diameters, depending on the fabricator's tooling investments. However, microvias are known to be prone to failure during plating, filling, and assembly, prompting the IPC to issue a warning about these reliability concerns in early 2019. To learn more about microvia fabrication, I encourage readers to look at this article on HDI manufacturing by Happy Holden.

Types of Microvias

There are a few different types of microvias. All microvias have two common characteristics:

- Low aspect ratio: Contrary to through-hole vias in typical PCBs, microvias have small aspect ratio. The aspect ratio of these vias is preferably 0.75:1. Larger aspect ratios of 1:1, or even as high as 2:1, can be fabricated, but they bring reliability concerns. Because of this, they typically only span between a single layer. Note that a microvia aspect ratio that is greater than 1 does not meet the IPC definition of a microvia.

- Susceptible to fracture at the neck: High aspect ratio through-hole vias (~10:1) tend to be most susceptible to fracture near the middle of the via barrel. Due to the plating method used in microvias, copper curves inward to the barrel region and stress tends to concentrate there. As a result, microvias are most susceptible to fracture in the neck region under repeated thermal cycling, strong vibration, or mechanical shock.

Aside from these qualities, the differences between microvias are simply their typical diameter and where they appear in a circuit board. Microvia-in-pad configuration is common with fine-pitch BGA components, where the small distance between solder balls will not allow a dog bone fanout. Microvias on the surface layer can also be placed in a pad, filled with a conductive epoxy or electrodeposited copper, and plated over with copper (this is the microvia analogue of via-in-pad plated over, or VIPPO, for standard via sizes). The in-pad configuration has advantages in that the pad is now solderable, but the internal fill and the copper wrap plating on the via are now the main reliability concerns.

With these points in mind, here are the different types of microvias:

Blind Microvias

Blind microvias start in the surface layer and terminate 1 layer below the surface, although they could terminate or 2 layers below the surface layer if the aspect ratio is kept low. If you need to span 2 layers, it's better to use stacked microvias (see below) or staggered microvias as these will be more reliable. Blind microvias could be filled or unfilled.

Buried Microvias

Buried microvias have basically the same structure as blind vias and span between two interior layers and do not reach either circuit board surface. Just like blind microvias, it's best the aspect ratio stays low and they span a single layer to ensure reliability and ease of fabrication. These vias are filled with copper, either using a plating process with pure copper or with a epoxy + copper resin to ensure a strong connection across the head of the microvia. It's important that the process being used for plating results in void-free structures to ensure maximum reliability.

Stacked and Staggered Microvias

You may be a bit hesitant to try incorporating lots of buried and blind vias into your designs, but the layer-by-layer process for forming low aspect ratio microvias makes them useful in stacked applications. Stacked microvias are simply stacks of buried vias, or a blind microvia stacked on top of buried microvias. This is the standard way to span between multiple layers in an HDI PCB. The internal buried microvias in the stack need to be filled with conductive paste and plated over to ensure strong contact as the next via in the stack is deposited and plated. The alternative to stacked microvias is staggered microvias, where microvias on successive layers are offset from each other.

The design decision that needs to be made with stacked and staggered microvias, as well as individual blind/buried microvias, is the aspect ratio to be enforced in the design. Stacking is also important due to potential failure at the interface between vias in a stack.

Filled or Unfilled?

Microvias can be either filled or unfilled with copper. For buried microvias, it's important to fill the via hole with copper, especially if there will be any stacking. If any voids are left over in the interior of the via plating, then the via will experience high stress concentration along the via wall, which could lead to premature fracture during reflow or during operation. Blind microvias can be left unfilled, and this was typical in the early days of microvia fabrication and implementation. If blind microvias will be used in-pad, then they should be filled with a standard process.

The manufacturer will use pure copper or an epoxy +copper resin for plating. The typical process normally begins with conformal plating, followed by pulsed plating to fill in the body of the microvia with solid copper and eliminate voids. Plating processes that do not use some additive in the filler material typically results in void formation inside the body of the plating volume. Even if the microvia body is totally filled with copper, the copper may concentrate along the walls and the top surface of the if additives are not used during plating. Conformal plating also contributes to an uneven deposition of copper along the via body, leading to voiding.

Reliability Debates

I mentioned above that there has been some debate around the reliability of individual blind/buried microvias and stacked microvias. In particular, the interface between microvias in a stack and the butt joint at any copper wrap plating are known to be points of failure. The exact time to failure appears to depend on several factors, including:

- The aspect ratio of each microvia in the stack

- The number of microvias in a stacked

- The size of any voids that form in the filling material during plating

- Copper plating thickness (either wrap plating or thickness of the via barrel) at the corner of the top pad/via hole

The reliability concerns center around thermal cycling. As the design is thermally cycled, including during assembly, the PCB substrate can expand and extert high stress on the thin copper plating used in a microvia. As a result, failure can occur at plated interfaces, meaning the interface between two stacked microvias, and at the interface between a via and its capture pad. The second most common location is at the knee (where copper slopes into the via at the top pad), particularly if some plating is removed and the remaining copper is very thin.

Some of the typical failure modes are shown below, specifically at the via/via or via/pad interface, as well as at the top of the via at the plating interface.

Although the specific criteria that can be used to concretely judge reliability are still unclear, there are a few points everyone seems to agree on:

- Smaller aspect ratios tend to be more reliable. In the paper from Lesniewski (see below), 0.7 aspect ratio microvias could survive accelerated life testing, while aspect ratio 1 microvias failed after only a few thermal cycles.

- Voiding appears to be related to failure, but this depends on the shape of the void, volume void fraction, and aspect ratio. One cannot make a general statement that voids always increase failure rate for all aspect ratios and void sizes.

- Due to inconsistencies in reliability of stacked vs. staggered microvias, it's generally accepted that there should be no more than two microvias in a vertically stacked arrangement; other microvias in a vertical interconnect should be staggered.

- The presence of copper wrap plating on the top portion does not appear to be related to failure, rather the plating thickness at the butt joint is a greater predictor of failure.

For more information, take a look at these references, as well as the article from Happy Holden I've linked above.

- Lesniewski, T. Effects of Dielectric Material, Aspect Ratio and Copper Plating on Microvia Reliability. Link.

- Heer, H., & Wong, R. Reliability of Stacked Microvia. Link.

- Birch, B. Reliability Testing for Microvias in Printed Wiring Boards. Link.

Space Advantages

Aside from some fabrication difficulties for less-advanced manufacturers, microvias are ubiquitous in HDI PCBs and they are responsible for saving space in these boards. For fine-pitch components in dense boards, they are required to ensure components can be packed into small spaces. Circuit board space is money, and microvias will help lower your costs. Aside from allowing more dense connections between layers and with smaller traces, they also allow you to save space by placing a via directly in-pad. Microvias-in-pad also save you space by making connections inside the pads of surface mounted technologies (SMTs). Microvias are especially well-suited for this because of their small form factor. Sometimes, normal vias are too large to fit inside pads for SMTs like fine pitch ball grid arrays (BGAs). Microvias can fit inside the pad without causing any fabrication issues.

In addition to BGA breakout, microvias-in-pad will fit inside the pads of even the finest pitch BGAs, and they can be even more useful in breakout channels. Even if you use microvias-in-pad to save surface space, you’ll still need lots of layers to get those trace elsewhere on the circuit board. Using microvias can increase escape path width, possibly letting you use fewer layers to breakout a BGA.

EMI Advantages

Microvias have had a major effect on signal integrity in HDI circuits. The fact that microvias carry smaller parasitic capacitance and inductance, simply due to their small size, is one factor that allows them to be packed closer together without increasing crosstalk and noise coupling strength. The smaller parasitics negatively compensate for the stronger electromagnetic field when HDI traces and microvias are closer together.

One of the big problems in high-speed circuits is signal radiation and reflection in vias. In addition, a resonance in a large via stub can couple with high field strength into a neighboring via. In essence, large vias make great high frequency radiating antennas, especially when a signal is allowed to resonate in a stub. A good way to reduce an antenna's power is to reduce its size. Microvias are basically like smaller antennas, so they will already have smaller emission and absorption cross section compared larger vias. Microvias are also made layer by layer, which means there won’t be any stubs. As they are implemented in thinner dielectrics, they are also closer to GND planes and will have greater shielding. All of these points are reasons microvias and HDI interconnects in general tend to have fewer problems with radiation.

How Large Should You Make Your Microvias?

As has been mentioned above, the appropriate size of your microvias depends in part on the aspect ratio, which then relies on PCB layer thickness to determine the microvia hole size. Microvias can be sized based on three factors:

- An aspect ratio target or limit which will help ensure reliability

- The dielectric layer thickness where the microvia will be used

- The maximum hole/pad sizes that can fit into a fanout routing scheme

When two of these factors are known, the third can be determined. If you take the DFM-centric approach to designing an HDI PCB, your fabrication house can tell you the upper limit on the aspect ratio for your microvias (Point #1), and from your layer thicknesses you could determine the microvia hole size. In the other approach, if you determine layer thicknesses first, you can can use the layer thickness and aspect ratio to get the microvia hole size.

I suggest to use a very simple process to determine the smallest required drill size for microvias assuming you are constrained by the ball/pad pitch in component packages:

- Determine the number of HDI buildup layers required and select a standard HDI stack-up.

- Determine the largest drill size that can be used in the tightest routing area in the PCB.

- Using the result from #2, and your aspect ratio limit, determine the required layer thickness

- Select a laser-drillable prepreg that reaches the layer thickness found in #3

The goal here is to match commercially available materials to the lower limit on hole size and pad size for your microvias without violating an aspect ratio limit. Note that you can still use larger microvias where needed as long as they can satisfy etching clearances in PCB fabrication.

Define Standard HDI Stackups and Microvias in Your ECAD Tools

No matter how you decide to size the microvias in your HDI PCBs, the microvias used in these designs will need to be defined within a standard HDI PCB stackup before they can be accessed within the routing tools in your PCB. To do this, it's best to select one of the standard HDI PCB stackups with a core/buildup layer arrangement as shown below. In these arrangements, the laser-drillable prepregs are placed on the outer layers so that microvias can be accessed for routing. Among the set of standard HDI PCB stackups used in a design, Type II and Type III are most common.

Once a stackup is selected, determine an appropriate upper limit on the aspect ratio to set the via size limit. The via size limit can be set in the design rules, and these limits can be set for specific layer pairs or via types.

Now that you’ve got microvias in printed circuit design covered, you need the right PCB design software to create your next HDI PCB. Altium can help you enhance your advanced HDI PCBs with microvias and a wide range of other tools. Altium delivers an unprecedented amount of integration to the electronics industry until now relegated to the world of software development, allowing designers to work from home and reach unprecedented levels of efficiency.