Substrate-Like PCBs Push the Limits of HDI

Miniaturization is an ever-present trend in today's electronics, with HDI PCB design and manufacturing techniques causing circuit boards to look a lot like integrated circuits. There is a specific type of PCB that blurs the line between an IC substrate and an HDI PCB, known as a substrate-like PCB. These PCB designs are intended to provide the same functions as an IC substrate and a PCB in a single assembly, making them an important integration platform in many products. The technology is not new, but it is becoming more accessible as ultra-HDI design capacity is starting to increase, even down to levels available for system prototyping and short-run fabrication of advanced products.

This particular class of PCBs actually has some compelling market growth that EDA companies and manufacturers should not ignore. The market for substrate-like PCBs is expected to grow at approximately 15% CAGR and reach $9.9 billion by 2030 as more devices push past the HDI regime. Will your next device need to have high enough densities to be considered a substrate-like PCB? Keep reading to see if you can make use of this technology.

Is It a PCB, HDI/ultra-HDI PCB, or an IC Substrate?

Substrate-like PCBs occupy a middle ground between an HDI PCB and an IC substrate. They can typically be categorized as ultra-HDI PCBs as was described recently by Tara Dunn. I've also written about this technology in another article. The technology is not new and is sometimes categorized as "chip-on-board," although this is an older term often referring to wire-bonded dies on PCBs fabricated in the standard subtractive process.

The difference between standard PCBs, UHDI PCBs, and substrate-like PCBs is summarized in the following table.

|

Standard PCB |

|

|

HDI/Ultra-HDI PCB |

|

|

Substrate-like PCB |

|

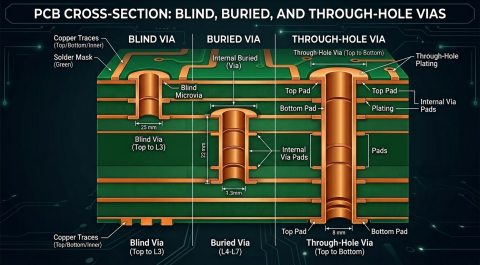

The differences between a UHDI PCB and substrate-like PCB should be quite clear: the UHDI PCB can have the same feature sizes and fabrication requirements as a substrate-like PCB, but the substrate-like PCB includes semiconductor dies with very fine pin pitch (flip chip or similar) which are bonded to the PCB, similar to chip-on-board.

One of the major drivers for the use of substrate-like PCBs has been smaller mobile devices or wearables, which need to pack many features into small spaces with fine-pitch components. This is of course the standard trend in HDI design, but IC substrates push the feature sizes and component densities to more extreme levels. Because a substrate-like PCB sits somewhere between HDI PCBs and IC substrates, I think it is worth comparing these types of components to see what capabilities are required for their fabrication. The image below shows this information as a spectrum, where we cross into the substrate-like PCB domain as linewidths get smaller. The feature sizes and layer counts listed below show how we can broadly categorize different types of ultra-HDI PCBs.

Eventually, as linewidths decrease, these products start to look more like IC substrates that provide interconnections between semiconductor dies (i.e., chiplets) inside a component package. This means we see:

- Higher trace densities (traces per unit distance)

- Change in fabrication processing to UV laserdirect imaging (LDI) or an additive process like SAP/mSAP

- Mixing of semiconductor dies/chiplets with standard off-the-shelf parts

- Multiple assembly processes required (see below)

- Semiconductors in substrate-like PCBs tend to be solder-bumped for flip-chip attach, but wirebonding can also be used

Assembly of Substrate-Like PCBs

Substrate-like PCBs may need to be assembled with multiple processes depending on the requirements of the dies being placed on the PCB. Because substrate-like PCBs integrate fine-pitch solder-bumped dies with off-the-shelf packaged components (e.g., in QFNs, SOIC, etc.) and even with through-hole components, multiple assembly processes could be required. The list of possible processes which might need to be mixed in a substrate-like PCB production environment is shown in the following table.

|

Through-hole parts |

|

|

Standard SMD packages |

|

|

Bumped dies |

|

The bumped die processes listed here (thermocompression bonding, thermosonic bonding, and ultrasonic bonding) are also used for wirebonding assembly. Wirebonding is not typically used in substrate-like PCBs, mainly because the goal of a substrate-like PCB is to implement high-density routing into a bumped semiconductor die. That being said, wirebonding is not forbidden in substrate-like PCBs, although it may be uncommon in commercial products that use these high-density assemblies. If wirebonding assembly will be included in substrate-like PCBs, some of the mechanical aspects can be automated inside your PCB design tool as shown in the demo below.

Once wirebonding is included, you will be forced into using a thermal/compression bonding process (thermocompression bonding, thermosonic bonding, or ultrasonic bonding).

Another option for increasing density in substrate-like PCBs is to use cavities for embedding one of the semiconductor dies and stacking the dies on top of each other. This could be performed with two dies of different sizes and density (smaller die embedded, larger die stacked on top) and when reliability with vertical die stacking (e.g., with through-silicon vias (TSVs)) is a concern. This is an approach that is sometimes taken with wirebonding, but the same approach could be used with solder-bumped dies normally used in flip-chip packages. This can be implemented in a PCB layout by defining appropriate footprints with pads that will attach to a solder bump array on the silicon die. An example possible stacking arrangement is shown below.

Here, the top die needs to have its bumps only arranged around the edges if the 2nd die is to be visible through L2. Otherwise, the 2nd die will need to be fully embedded in an internal layer. Underfill and encapsulation would be recommended on both parts to ensure reliability.

To define cavities in the PCB layout, you will need to either define cavity regions in a die footprint or place mechanical layers and layer-specific keepouts showing cavity regions in specific layers. ECAD software offers various options for performing this task, but Altium Designer enables either approach with its standard feature set. The video below shows a CAD-agnostic approach that anyone can used to define cavities using mechanical layers and cutouts.

Major Users of Substrate-Like PCBs

While the concept of these designs might be new to some designers, these components are not actually new. The substrate industry was dealing with the same challenges many years ago, they were just dealing with direct mounting of semiconductor dies onto a substrate rather than a mix of traditionally packaged components. Substrate-like PCBs essentially target any application using very fine chip-scale packaged ICs that must coexist with traditional ICs on the same substrate. You could also integrate chip-on-board into these packages.

One of the major users of substrate-like PCBs is smartphones, and the products available to consumers today are using substrate-like PCBs. The first instance of smartphones using substrate-like PCBs began in 2017 with the iPhone 8/X, which were fabricated with an mSAP process. Samsung also used the technology in their newer Galaxy line of smartphones.

Given the finite enclosure size, and the demand for more features with a bigger battery, the push is of course to decrease feature sizes on the chips and the PCB. The next generation of substrate-like PCBs is stacked assemblies, where very thin devices are packaged on top of each other with vertical interconnects.

Why Layer Counts Can Decrease at Higher Densities

If you look at the above spectrum, it would appear that substrate-like PCBs and IC substrates could have lower layer counts than a traditional HDI PCB. This might seem contradictory at first, especially if you compare standard HDI PCBs with lower density PCBs built using the standard etching process. What happens when crossing the HDI-to-substrate-like PCB threshold?

The first reason is the materials being used in these designs. Materials used in these boards can be much thinner, both for rigid and modified polyimide substrate-like PCBs. Thinner layers mean two things that are important for achieving higher densities:

- The width needed for controlled impedance lines is smaller on thinner layers

- The spacing between digital lines can be smaller (below the 3W limit) when ground is interleaved between signal layers

I’ve discussed these points in a past article on thick vs. thin FR4 layers, as well as a blog on low-Dk dielectrics.

The other reason is the manufacturing process, which can fabricate well below sub-40 micron linewidths and spacings. Once we decrease the linewidth and spacing to very small values, there will start to be an increase in crosstalk, which myself and a colleague from Thintronics have called the "crosstalk penalty" at high densities. Therefore, we have to look at the factors affecting signal integrity in these designs to see how we can overcome crosstalk penalty when taking advantage of miniaturization.

Signal Integrity in Dense Substrate-Like PCBs

The 2nd point above deserves explaining because less-advanced PCBs will often use less than 3W spacing between digital lines without experiencing excessive crosstalk, particularly in interfaces like SPI where there is no impedance specification and the lines can be quite wide. However, if you take a PCB with a specific L/S value, and you scale this down to the level required for UHDI/substrate-like PCB routing into component dies, you will experience a crosstalk penalty and the spacing (S) value will need to increase.

Suppose you have a PCB with 1.5W spacing between digital lines; if you were to scale those connections down to very thin lines on a substrate-like PCB with the same 1.5W spacing on a thin substrate, you will experience a very large increase in density, but you will get higher crosstalk for the same 1.5W value. If you were to increase the spacing on the substrate-like PCB to, e.g., 2W, then you can bring the crosstalk back to the prior value while still seeing a large increase in density.

A simple S-parameter simulation at each spacing and layer thickness value will help determine the appropriate spacing value required in your design. To learn more, read the following article on UHDI signal integrity as the same points apply to substrate-like PCBs.

When you need PCB design software that scales down to smaller feature sizes, use the complete set of CAD features in Altium Designer® to build your most advanced products. When you’ve finished your design, and you want to release files to your manufacturer, the Altium 365™ platform makes it easy to collaborate and share your projects.

We have only scratched the surface of what’s possible with Altium Designer on Altium 365. Start your free trial of Altium Designer + Altium 365 today.