Integridad de señal en capas ultrafinas de PCB HDI

La integridad de la señal de PCB comienza a cambiar cuando se observa lo que sucede en las capas ultrafinas de PCB utilizadas en PCBs HDI y ultra-HDI.

Para mí parece que cada artículo sobre "diseños avanzados" se centra en tasas de cambio rápidas, pero a menudo deja de lado la miniaturización. Los diseños HDI llevan a las PCBs a un espacio de solución donde las reglas de integridad de señal comienzan a cambiar debido a las escalas de longitud involucradas en un diseño típico. Una clase importante de materiales ha habilitado los diseños HDI y UHDI con grandes cantidades de interfaces de alta velocidad: los laminados de PCB de bajo Dk. La historia de HDI está vinculada a la historia de los materiales de PCB de bajo Dk, especialmente una vez que una placa HDI implementa muchas interfaces digitales de alta velocidad.

Una vez que miras los sustratos de IC y los materiales típicos utilizados en estos diseños, encontrarás los mismos tipos de materiales de bajo Dk que habilitan muchos diseños digitales de alta velocidad, y quizás aquí es donde el mundo de las PCBs obtuvo la idea para los materiales de PCB de bajo Dk.

Los diseños HDI más nuevos empujan el enfoque HDI convencional al límite, conocido mejor como ultra-HDI o UHDI. En estos diseños, las pequeñas características de cobre se convierten en un factor importante que limita el ancho de banda del canal para interconexiones de alta velocidad, pero los materiales de bajo Dk combinados con cobre más suave e innovadores recubrimientos ayudan a superar estos problemas.

En esta breve serie de blogs, daré una visión general de cómo la integridad de señal se relaciona con el tamaño de las capas y características en PCBs HDI/UHDI, lo cual veremos que está estrechamente relacionado con canales de alta banda ancha en empaquetado. Para comenzar, revisaremos los beneficios de manufacturabilidad de ciertos materiales de baja Dk.

Manufacturabilidad con Materiales de Baja Dk

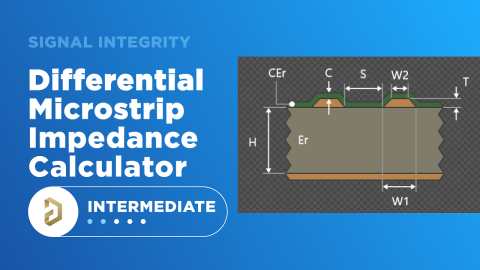

El primer punto importante a tener en cuenta respecto al uso de materiales de baja Dk es la manufacturabilidad de tamaños de características HDI/UHDI como función del valor Dk del laminado. Echa un vistazo al gráfico a continuación para ver a qué me refiero.

Para un objetivo de impedancia de traza dado (digamos, 50 Ohmios), el ancho de la traza se fijará en algún valor que es una función del grosor del laminado. Cuando el laminado se vuelve demasiado delgado, el requisito de ancho de traza será demasiado delgado, y el proceso de grabado del cobre se volverá más costoso, eventualmente cambiando a procesamiento aditivo. El gráfico a continuación resume esta tendencia para valores Dk bajos y altos.

El contrapunto a esto es el hecho de que no todos los materiales de baja Dk (como Dk = 3 o ligeramente menos) están disponibles en espesores de película muy pequeños requeridos para PCBs UHDI o sustratos IC. Los materiales de baja Dk que llegan hasta unos pocos mils con refuerzo de vidrio esparcido están disponibles con valores de Dk cercanos a 3 y aproximadamente Df = 0.001. Ejemplos son Megtron 8 y Tachyon 100G.

Tenga en cuenta que esto es más delgado que un laminado avanzado de PTFE como Rogers 3003, pero opera en el mismo rango de PTFE avanzado con Dk = 3 o menos con Df

Qué Sucede con la Integridad de la Señal en Capas Delgadas

Basándonos en la breve discusión sobre materiales que he presentado arriba, podemos usar esta información para entender mejor la relación entre las propiedades de los materiales, el grosor de los laminados y la integridad de la señal. Comenzamos con algunos hechos sobre los materiales y la geometría de las pistas en las capas HDI/UHDI, especialmente cuando el número de capas se vuelve alto:

- Las capas más delgadas obligan a que las trazas de impedancia controlada sean más pequeñas

- Las capas más delgadas generalmente acercan los planos de tierra a las trazas

- Los patillajes de los dispositivos (por ejemplo, BGAs de paso fino) pueden obligar a que las trazas estén más juntas

- Los materiales (cobre y valor Dk) se pueden utilizar para ajustar la métrica de integridad de señal

Cuando llegamos a dispositivos UHDI, también podríamos decidir omitir planos en ciertas capas, creando esencialmente un enrutamiento de capas saltadas como se utiliza en canales digitales de alto ancho de banda en sustratos de IC. Hablaré más sobre esto a continuación. Primero, veamos algunas de las métricas básicas importantes, comenzando con las pérdidas y las impedancias.

Pérdidas de Cobre vs. Dieléctricas

Cuando se opera en placas HDI y UHDI, los patillajes de los dispositivos y los requisitos de impedancia requieren que los anchos de las trazas sean más pequeños, tanto para el enrutamiento de salida de los BGAs como para el enrutamiento de impedancia controlada. Esto podría hacer que el mecanismo de pérdida dominante cambie de dieléctrico a cobre cuando se utiliza un Dk más bajo.

Por ejemplo, echa un vistazo a los datos de pérdida de microstrip a continuación en un laminado FR4 algo avanzado. Las pérdidas en el gráfico a continuación se trazan como el factor de atenuación de voltaje (vea aquí para más detalles). El grosor de FR4 es de 38 micrones (1.5 mil), los datos del material son (Dk = 4, Df = 0.01, grosor), y la capa utiliza cobre de 1 oz. con una rugosidad de 1 micrón. Un microstrip de 50 Ohm tendrá 57 micrones de ancho.

Pérdida de cobre versus pérdida dieléctrica para un microstrip de 50 Ohm y 57 micrones de ancho en Megtron 7(G) (Dk = 4, Df = 0.01) y 1 micrón de rugosidad de cobre.

Ahora supongamos que el material laminado se reemplaza con una hoja de Megtron 7(G) (Dk = 3.37, Df = 0.001) con el mismo grosor de 38 micrones (1.5 mil). El microstrip de 50 Ohm ahora requiere un ancho de 68 micrones. La gran reducción en la pérdida dieléctrica ahora hace que la pérdida de cobre sea el factor dominante hasta frecuencias muy altas.

Pérdida de cobre versus pérdida dieléctrica para un microstrip de 50 Ohm y 65 micrones de ancho en Megtron 7(G) (Dk = 3.37, Df = 0.001) y 1 micrón de rugosidad de cobre.

Cuando comparamos microstripes y striplines, podemos ver la penalización por pérdida y los valores de ancho de línea dados los requisitos de espesor de capa para una línea de 50 Ohmios de extremo único. He incluido un material hipotético con Dk = 2 en espesores de HDI/UHDI para comparación y para proporcionar un límite teórico. Se pueden derivar resultados similares para líneas diferenciales.

Podemos ver claramente una divergencia no lineal en la pérdida para estos trazos de extremo único una vez que bajamos aproximadamente a espesores de capa de 2 mil para todos los materiales (Dk = 2 hasta aproximadamente Dk = 3.5). Esto se debe a la relación inversa entre la resistencia por efecto pelicular y el ancho del trazo.

La conclusión: Usar un Dk bajo ayuda con las pérdidas totales en placas HDI/UHDI al forzar un ancho de trazo más amplio y reducir la pérdida dieléctrica, pero en algún punto la pérdida de cobre comienza a dominar, y obtienes rendimientos decrecientes en tu inversión en costos de materiales laminados. La reducción de la rugosidad del cobre será la única manera de continuar reduciendo la pérdida total.

Problemas de Chapado

Se pueden lograr reducciones adicionales en la pérdida de conductores utilizando recubrimientos superficiales alternativos y láminas de cobre más lisas. Por ejemplo, es bien sabido que los recubrimientos basados en níquel pueden rugosizar el cobre en las interfaces de recubrimiento y crear pérdidas magnéticas (como en los recubrimientos ENIG y ENEPIG). La investigación sobre recubrimientos más avanzados está en curso y los problemas de recubrimiento son un área activa de discusión para las PCBs UHDI, tanto desde el aspecto de integridad de señal, como desde el aspecto de fabricación (DFM/DFA).

Para aprender más sobre este problema con los recubrimientos, mira nuestro reciente episodio de podcast con Kunal Shah.

Penalización por Diafonía

Cuando se toma un diseño con enrutamiento de trazas existente y se escala hacia niveles HDI/UHDI, las trazas se acercarán más y se esperaría más diafonía. En algún punto, la densidad de las trazas podría requerir que vayas por debajo de una regla conservadora de diafonía, más comúnmente la regla de “3W”. Sin embargo, la tierra se verá forzada a acercarse más a las trazas cuando el número de capas sea mayor, y se esperaría que esto reduzca la diafonía. ¿Cuál efecto predomina en un diseño UHDI?

La respuesta depende de varios factores:

- ¿Estamos usando pares diferenciales y por lo tanto en riesgo de diafonía multimodo?

- ¿Estamos enrutando líneas de transmisión desplazadas o microtiras desplazadas?

- ¿Estamos utilizando laminados de alta o baja constante dieléctrica (Dk)?

Cuando se reduce la escala a UHDI, podría haber una penalización por diafonía, lo que significa que la diafonía podría aumentar a medida que se empaquetan las pistas más cerca unas de otras. Tu trabajo como diseñador es reducir la penalización por diafonía ajustando el grosor de la capa y el valor de Dk. Para entender mejor los efectos de la diafonía, necesitamos utilizar simulaciones de S-parámetros multi-puerto para comprender mejor cómo se relaciona la diafonía con el valor de Dk del laminado y el grosor del laminado.

Los espectros de S-parámetros diferenciales mostrados a continuación ilustran las diferencias en los niveles de diafonía al cambiar de un laminado Megtron 7 (grosor de 3 mil, Dk = 3.37) a un laminado Megtron 8 (grosor de 1.5 mil, Dk = 3.06). Estos resultados fueron simulados en Simbeor en líneas de transmisión diferenciales simétricas de 100 Ohm (espaciado entre pistas = ancho) mientras se variaba el espaciado entre pares de 2W a 3W.

Espectros de diafonía de línea de transmisión simétrica diferencial: la curva azul muestra NEXT, la curva roja muestra FEXT.

Como podemos ver en el resultado anterior, cambiar al laminado Megtron 8 de 1.5 mil más delgado con un espaciado de laminado de 3W aumenta el crosstalk máximo al 4.38%. Si simplemente cambiamos de Megtron 7 de 3 mil a Megtron 7 de 1.5 mil manteniendo todos los demás parámetros iguales, el crosstalk máximo sería del 6.82%.

Lo interesante aquí es que cuando cambiamos de un espaciado de 2W en Megtron 7 de 3 mil a un espaciado de 3W en Megtron 8 de 1.5 mil, vemos una penalización de crosstalk menor, como se esperaba. Uno podría suponer que cambiar de 2W a 3W de espaciado da como resultado una disminución en la densidad de enrutamiento, pero este no es el caso. Todavía vemos un aumento en la densidad de trazas del 108% al cambiar al laminado Megtron 8 más delgado, a pesar del menor Dk. Los espectros de pérdida de retorno para estos interconectores muestran una reducción de ancho de banda de solo el 20% tanto para el laminado Megtron 7 de 1.5 mil como para el laminado Megtron 8 de 1.5 mil.

La conclusión: Para superar las penalizaciones por diafonía con un valor de espaciado entre pistas (o entre pares) dado (como S = 2W), puede ser necesario aumentar el espaciado en el laminado más delgado, y puede que sea necesario cambiar la constante dieléctrica. Sin embargo, esto no siempre significa que la densidad de enrutamiento de tus pistas disminuya. A partir del ejemplo anterior, todavía tenemos un doblamiento de la densidad de enrutamiento, a pesar de usar un valor de Dk menor. Resultados muy similares pueden derivarse para pistas de extremo único.

Enrutamiento de Capas Saltadas y Enrutamiento de Líneas de Transmisión Desplazadas para Altos Anchos de Banda

La mayoría de las PCBs UHDI y los sustratos de IC contendrán canales que no son de ancho de banda extremadamente alto. La mayoría de los pines serán para alimentación, tierra, configuración, GPIO e interfaces seriales más lentas. Sin embargo, en procesadores con PCIe, DDR, múltiples interfaces USB y enlaces SerDes rápidos, el enrutamiento en el sustrato y la PCB será diferencial con un

Dos estilos de enrutamiento muy similares están disponibles para el enrutamiento de pares diferenciales en PCBs UHDI y sustratos de IC. Estos son:

- Enrutamiento de capas saltadas en sustratos IC (no confundir con vías de capas saltadas)

- Enrutamiento de línea de banda desplazada en PCBs HDI

Estos dos son básicamente el mismo tipo de enrutamiento, pero el enrutamiento de capas saltadas utiliza una barrera de vías para separar interconexiones en un sustrato. Hay dos razones para usar la barrera de vías en el enrutamiento de capas saltadas: para proporcionar efectividad de blindaje contra el diafonía entre pares y para establecer la frecuencia de corte del modo TEM más allá de la frecuencia de Nyquist de la interfaz receptora.

Cuando pasamos a capas dieléctricas más delgadas con líneas de banda (ver arriba), tenemos una penalización por diafonía entre estas trazas. Sin embargo, con el enrutamiento de capas saltadas, podrías reducir la penalización por diafonía añadiendo la capa dieléctrica entre los pares como se muestra en la disposición anterior.

Si la diafonía entre estas señales sigue siendo problemática, la reducción de la diafonía podría requerir cualquiera de lo siguiente para reducir la diafonía:

- Aumentar la densidad de la valla de vías

- Disminuir la extensión de las vías a través de un canal (puede aumentar el ancho de banda del canal)

- Cambiar el dieléctrico por uno con diferente Dk

- Cambiar el espaciado entre pistas en el par

En sustratos IC y PCBs UHDI, cualquiera de estos cambios debería ser simulado y puede producir una disminución en la penalización por diafonía, tal como muestro arriba en la sección de diafonía. Sin embargo, estos cambios podrían enfrentarse a limitaciones de fabricación, incluso en el caso de que un dispositivo sea fabricado con un proceso aditivo. Cuando se alcanzan las limitaciones de fabricación, podría ser necesario cambiar el valor de Dk para los laminados.

Ancho de Banda del Canal a Alta Velocidad

No todas las interfaces en PCBs HDI/UHDI y sustratos requerirán límites de ancho de banda TEM extremadamente altos. Pero cuando lo hacen, podría haber una penalización en el ancho de banda del canal al cambiar a una capa más delgada. Esto podría resultar de un aumento en las pérdidas de cobre, lo que crea una desviación de impedancia del valor objetivo de interconexión a frecuencias más altas debido al efecto piel.

Sin embargo, dependiendo del valor Dk del laminado, la carga y el tipo de canal, cualquier limitación en el ancho de banda del canal podría ocurrir a una frecuencia tan alta que resulte insignificante, o podría haber un aumento en el ancho de banda del canal. Esto no es tan importante en interfaces como MIPI o USB, pero tiene gran importancia en DDR4/5/6, PCIe 5.0 o superior, y Ethernet de 25G o más rápido. Estudiar el ancho de banda del canal requiere observar los límites de ancho de banda TEM en guías de onda coplanares, como en las placas RF, algo que planeo presentar con más detalle en el futuro.

Ya sea que necesite construir electrónica de potencia confiable o sistemas digitales avanzados, utilice el conjunto completo de características de diseño de PCB y herramientas CAD de clase mundial en Altium Designer. Para implementar la colaboración en el entorno interdisciplinario de hoy, las empresas innovadoras están utilizando Altium 365 para compartir fácilmente datos de diseño y poner proyectos en fabricación.

Solo hemos arañado la superficie de lo que es posible con Altium Designer en Altium 365. Comience su prueba gratuita de Altium Designer + Altium 365 hoy.