設計データ管理

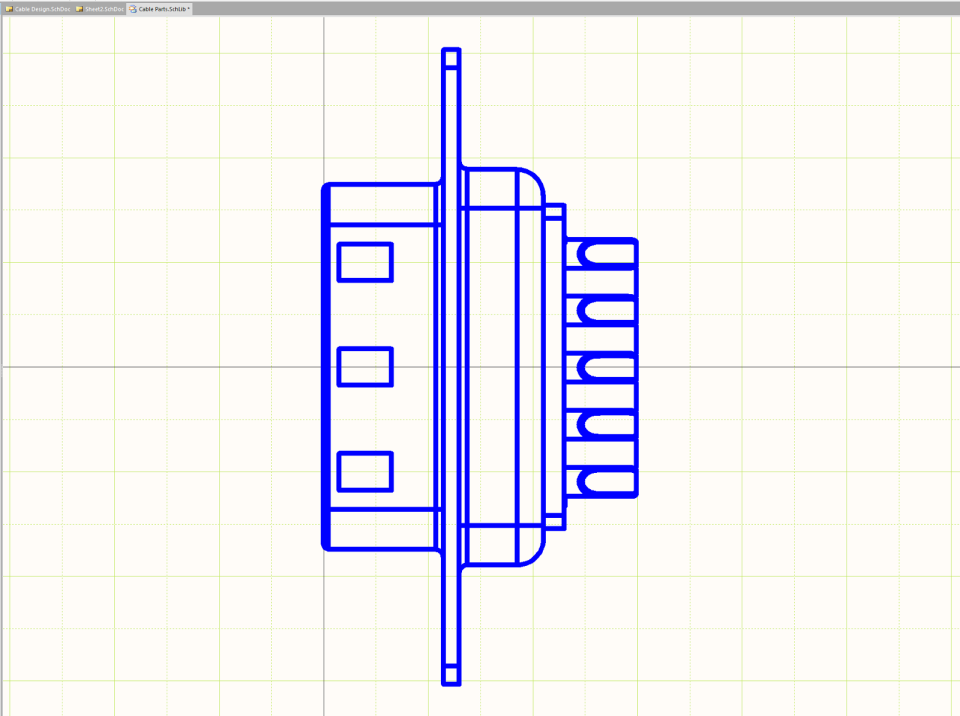

設計プロセスでは、設計フェーズの終了後も有効期限がある多くのデータが生成されます。アルティウムでは、設計データの長期および短期の安全な保存と、この設計データが将来のより効率的な設計に貢献できるようにする方法を提案しています。PCB設計データ管理に関するリソースライブラリをご覧ください。

Filter

見つかりました

Sort by