メモリ不足下でのハードウェア設計:エンジニアと調達チームのための実践ガイド

このシリーズの第1回、AIがメモリ市場をどう変えたかでは、AIデータセンター需要によってメモリがボトルネック化した経緯と、DRAMおよびNANDの価格が短期間では正常化しにくい理由を見てきました。今回は、この環境下でどう対応すべきかを掘り下げます。2026年にハードウェアを設計または調達するのであれば、依然として判断すべきことがあります。どの部品を採用仕様にするか、柔軟性を持たせるために設計をどう構成するか、そしてサプライチェーンリスクをどう管理するかです。

まず、今後の方向性を示す「次の波」のメモリ部品を取り上げ、その後で主力となるDRAMおよびフラッシュ部品を見ていきます。さらに、エンジニアリング部門と調達部門の双方に向けた実践的なプレイブックを提示します。

メモリ部品を幅広く調べる出発点としては、Octopartのmemory ICsおよびflash memoryのカテゴリーページが有用です。メーカー、パッケージ、供給状況を横断して検索できます。

重要なポイント

- 今後登場するものと、今入手できるものを見極めること。 LPDDR6やHBM4のような次世代部品はプラットフォームの進む方向を示していますが、2026年の製品設計で実際に出荷に使われるのは、DDR5、LPDDR5X、そして現在在庫のある成熟したNANDです。

- 代替可能性と柔軟性を前提に設計すること。 主流インターフェースを標準採用し、部品ファミリを認定し、ファームウェアで複数の容量をサポートしましょう。可能な限りソケットやモジュールを使い、UX目標を満たせる範囲で選別落ちメモリの選択肢も計画しておくべきです。

- 供給リスクは工学的課題として扱うこと。 複数ソースのAVLを構築し、重要ラインの割当を確保し、ライフサイクルを追跡し、Octopartのようなツールで代替品を管理しましょう。

方向性を示す次世代コンポーネント

SamsungのLPDDR6モバイルDRAM

オンデバイスAI、自動車、次世代モバイルおよびPCプラットフォーム向けに設計されたSamsungのLPDDR6は、LPDDR5Xに対して大きな効率向上、拡張されたI/Oアーキテクチャ、そして最大10.7Gbpsの初期速度を実現します。さらにLPDDR6規格自体も、エコシステムの成熟に伴って今後さらに拡張されるよう設計されています。現時点ではLPDDR6がディストリビュータの棚に並ぶことはまだありませんが、先進的なSoCやフラッグシップ機器を前提に設計するなら、これに直面することを想定しておくべきです。

HBM4

スタックの最上位では、SK Hynixの16層・48GB HBM4デバイスが2TB/s超の帯域幅を約束しており、量産開始は2026年第3四半期ごろが目標とされています。Samsungは異なるアプローチを採っており、4nmロジックと1c DRAMを用いて熱性能の改善を図っています。AIハードウェアに携わるエンジニアでも、通常これらをカタログ系ディストリビュータから調達することはありません。しかしHBM4は誰にとっても重要です。というのも、先端DRAM生産能力の大きな割合を吸収しており、それが従来型DRAMの供給逼迫が続く理由の一つだからです。

Samsung第10世代V-NAND

400層超と5.6GT/sインターフェースを備えるSamsungの第10世代V-NANDは、データセンターおよびAIクラスのワークロード向けに、PCIe 5.0および将来のPCIe 6.0 SSDをターゲットとしています。このシリコンをベースにした高密度TLCは、今後数年にわたり多くのエンタープライズ向けおよびハイエンドクライアント向けドライブの基盤になると見込まれます。

Kioxia/Sandisk BiCS10 NAND

この332層BiCS10は、Toggle DDR 6.0インターフェースによりピン当たり4.8Gb/sを実現し、AIおよびハイパースケールストレージをターゲットとしています。EE Timesによると、Kioxiaは2026年のNAND生産分がすでにすべてAI関連用途向けに売約済みであると述べており、需要に対応するためBiCS10の立ち上げ時期を2027年後半から2026年へ前倒ししました。

比較的制約の少ない主力メモリ製品

以下の部品は、2026年3月上旬時点で主要ディストリビュータから注文可能でした。供給状況は急速に変化しているため、BOMを確定する前にOctopartで在庫とライフサイクル状況を確認してください。

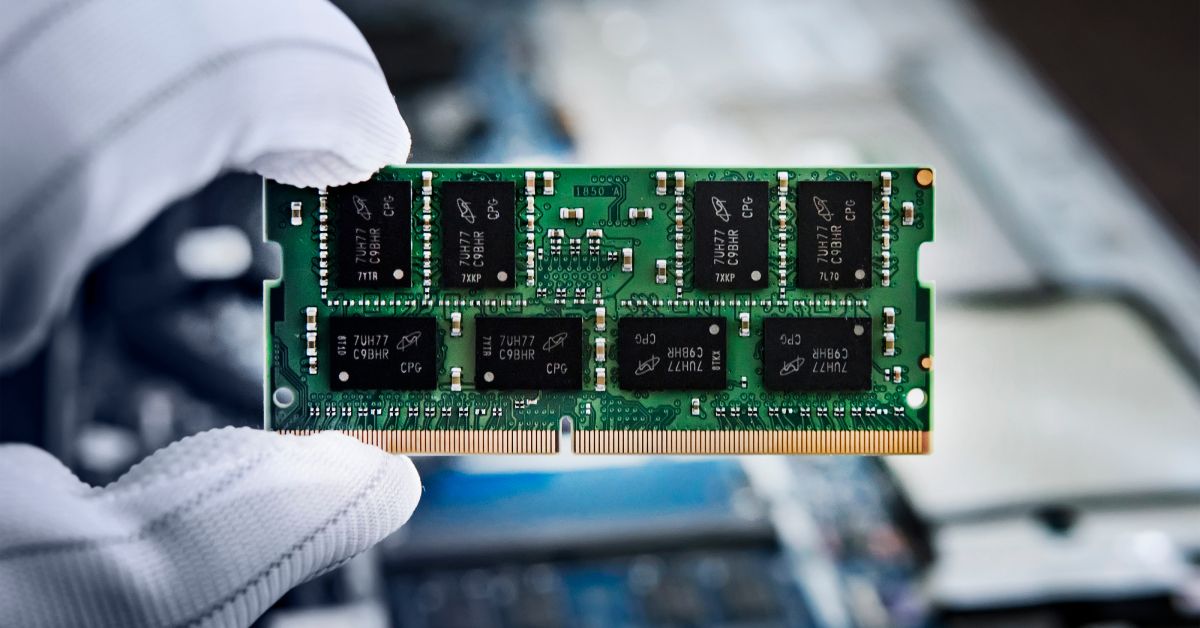

- Apacer D22.31491S.001、8GB DDR5-4800 SO-DIMM。 ソケット式モジュールを使える設計にとって実用的な「後付け選定」型のDRAMオプションであり、調達時の代替対応力を高められます。

- MT60B2G8RZ-56B IT:D、16Gbit DDR5 SDRAM(2G x 8)、78ボールVFBGA。 カスタム基板レベルのメモリ設計に適した主流のx8 DDR5-5600クラスDRAM ICで、単独モジュールSKUよりも現実的なセカンドソースの柔軟性を確保できます。

- Macronix MX30LF4G28AD-XKI-TR、4Gbit SLC NAND(VFBGA-63)。 耐久性と予測可能な動作が求められる産業機器および組み込み向けNAND設計に適しており、コンパクトなBGAフットプリントにも収まります。

- Macronix MX60LF8G28AD-TI-T、8Gbit SLC NAND(TSOP-48)。 成熟したコントローラエコシステムに対応する広くサポートされたパラレルNANDフットプリントが必要で、細ピッチBGAより基板リワークを容易にしたい場合に実用的な選択肢です。

- Macronix MX52LM04A11XSI、4GB eMMC 5.1(BGA-153)。 コントローラ依存性を減らし、生NAND+独自フラッシュスタックよりもすっきりした代替対応を望む場合に、扱いやすいマネージドNANDの選択肢です。

- Macronix MX52LM08A11XVW、8GB eMMC 5.1(BGA-153)。 多くの組み込みLinux機器やHMIクラスのシステムにとって実用的な容量帯であり、小容量eMMC部品と同じインターフェースおよび統合上の利点を備えています。

- Micron MT40A2G8SA-062E:F、16Gbit DDR4 DRAM(2G x 8)。 依然として多くのプラットフォームで大量採用される主力製品であり、DDR5が必須でない場合には現実的な「今すぐ出荷できる」選択肢です。

設計プレイブック:エンジニアが柔軟性を組み込む方法

このような状況下でも、ハードウェアエンジニアが設計のレジリエンスを高めるために取れる行動は数多くあります。

- 主流インターフェースと主流ファミリを標準採用する。 DDR5、LPDDR5X、e.MMC、UFS、SPI/QSPIフラッシュは、エコシステムが厚く、セカンドソースも豊富です。一般的な電圧とパッケージに収めることで、互換部品の候補を最大化できます。

- ファームウェアとメモリマップに柔軟性を持たせる。 DRAM容量やSPIフラッシュ容量を単一値でハードコードするのは避けましょう。初期化コードで複数のジオメトリをサポートすれば、代替品への差し替えが可能になります。

- 適合するならマネージド不揮発性メモリを優先する。 e.MMCやUFSは、安定したインターフェースの背後にNAND管理の詳細を隠してくれるため、特定コントローラに強く結び付いた生NANDよりも代替パスが明確なことが多くあります。

- 選別落ち品を前提としたバリアントを計画する。 低メモリ構成でも許容可能なユーザー体験を提供できるようにソフトウェアを設計しましょう。たとえば、デフォルト同時実行数を減らす、アセットセットを小さくする、機能を階層化するといった方法があります。

- 可能な限りモジュール型のメモリとストレージを使う。 SO-DIMM、UDIMM、M.2 SSD向けソケットを使えば、構成を後段で決められ、調達側の交渉力も高まります。はんだ実装メモリは、本当に必要な制約の厳しいフォームファクタに限定しましょう。

調達プレイブック:調達部門がリスクを管理する方法

この状況は見過ごせません。2026年2月下旬、Lenovoはチャネルパートナーに対し、3月の値上げを回避するため月末までに発注するよう警告しました。一方で、TrendForceは、PC向けDRAM(DDR4/DDR5)の平均価格が第1四半期だけで前四半期比105~110%上昇すると予測しました。以下のプレイブックは、この新しい現実を反映したものです。

- 重要なDRAMおよびNANDラインについては、割当確保と長期契約を進めること。特にサーバー、AIボックス、ハイエンドノートPC向けでは重要です。TrendForceのような調査会社の市場インテリジェンスは、いつコミットすべきかの判断材料になります。

- 承認ベンダーリストは個別SKUではなくファミリ単位で構築する。

許容可能なモジュール、NAND、e.MMCのクラスを定義し、複数の選択肢を事前にエンジニアリング部門と連携して検証しておきましょう。 - 製品をメモリ感応度で分類する。 希少で高価なメモリは、性能や利益率への影響が大きいSKUに優先配分し、メモリ依存度の低い機器にはより積極的なコスト管理を適用します。

- 長寿命製品では、メモリ在庫を戦略的ヘッジとして活用する。 主要なDRAMやNANDをバッファ在庫として持つ方が、部品が逼迫した際に製品ライフ途中で基板再設計やファームウェア書き換えを行うより安く済む場合があります。

柔軟性こそが戦略

このシリーズの第1回では、メモリ逼迫の背景にある理由を説明しました。そして今回は、「では今どうするか」を見てきました。エンジニアであっても調達担当であっても、答えは同じです。最良のヘッジは柔軟性です。代替を前提に設計し、広く認定を取り、Octopartのようなツールを使って選択肢を可視化し、常に最新状態に保ちましょう。この局面を最も良い形で乗り切るチームは、設計とサプライチェーンの両方に早い段階から選択肢を組み込み、供給と価格の変化に応じて適応し続けるチームです。

よくある質問

2026年になってもDRAMとNANDの調達が難しいのはなぜですか?

現在の不足は、技術的限界ではなくウェハ割当によって引き起こされています。メモリベンダーは、特にHBMやデータセンター向けDRAMといった高利益のAI需要を、複数年契約のもとで優先しています。HBMは従来型DRAMに比べてビット当たりではるかに多くのウェハ能力を消費するため、DDR5、LPDDR、NANDに回る能力が減り、供給逼迫が続いています。

エンジニアは今、LPDDR6やHBM4のような次世代メモリを前提に設計すべきですか?

LPDDR6やHBM4はプラットフォームの進む方向を示していますが、2026年の製品の大半は、現在入手可能なDDR5、LPDDR5X、成熟したNANDで出荷されます。エンジニアは将来互換性を意識して設計しつつも、まだ流通に乗っていない部品に賭けるのではなく、生産時に確実に調達できる部品を選定すべきです。

メモリ不足に強いハードウェア設計にするにはどうすればよいですか?

強靭な設計は、柔軟性と代替可能性を重視します。具体的には、主流インターフェースの標準採用、複数容量や複数ベンダーの認定、ファームウェア内での固定的なメモリ前提の排除、可能な限りのソケットやモジュールの活用などが含まれます。選別落ちメモリの選択肢にも対応しておけば、高容量部品が逼迫した場合調達部門は、メモリをコモディティではなく戦略的資源として扱うべきです。ベストプラクティスとしては、重要なSKUについて長期的な割当を確保すること、単一部品ではなく製品ファミリーを軸にAVLを構築すること、Octopartのようなツールでライフサイクルや代替部品を監視すること、そして長期ライフサイクル製品については強制的な再設計を避けるために在庫を選択的に保有することが挙げられます。