高速バスの長さを一致させる方法

投稿日 2020/09/28 月曜日

高速データシステムの高速化に伴い、いくつかのPCBレイアウトの課題が出てきます。DDR、VME、PCIeのような高速バスは、非常に厳しい公差で厳密なタイミングを必要とするデータ転送速度に達することができるため、PCBレイアウトにおける余裕はありません。

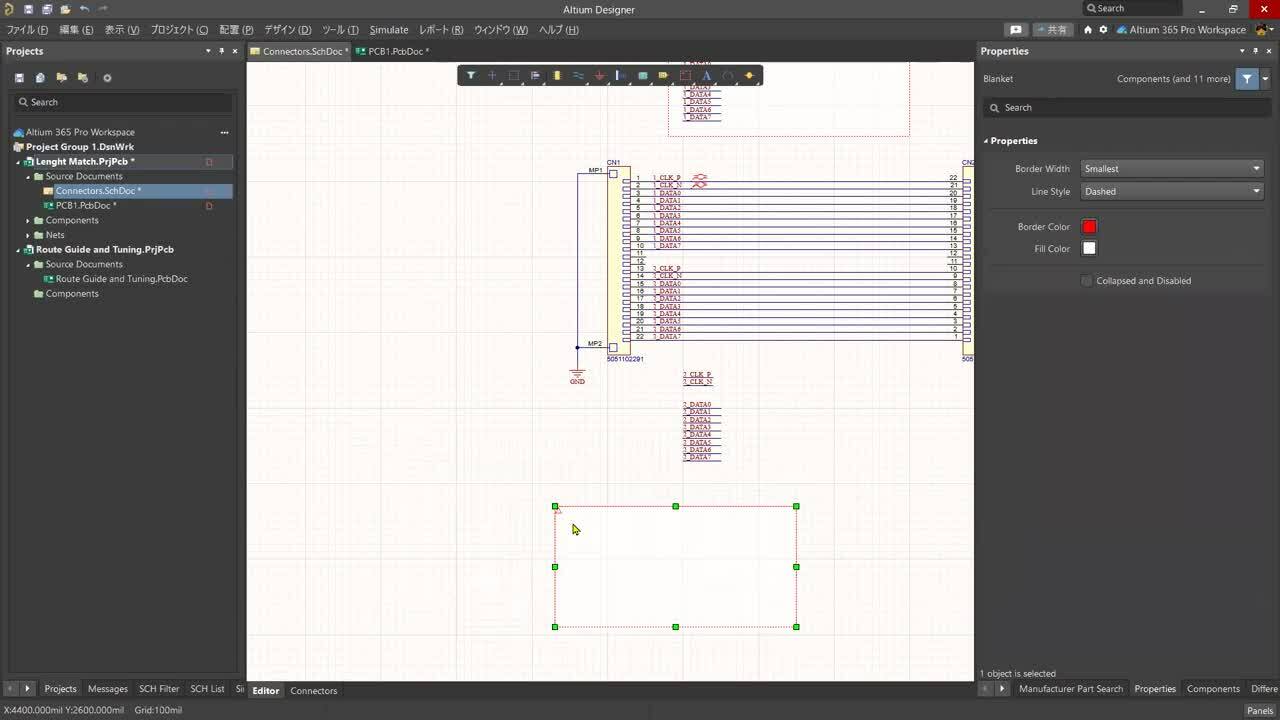

このオンデマンドWebセミナーでは、なぜ高速データシステムと差動信号でトラックの長さを一致させることが重要である理由について解説します。PCBの長さのマッチングと時間遅延の制約を適切に定義する方法、そしてAltium Designer®で高速信号を効果的に配線する方法について学ぶことができます。

以下は、セッションで紹介されたトピックとなります。

-

なぜ高速信号でトラックの長さを一致させることが重要なのか?

-

高速バスや差動信号での長さ合わせや時間遅延チューニング

-

回路図やPCBから高速PCB制約ルールを設定する方法

-

シングルエンドおよび差動トラックのチューニング方法

今すぐAltium Designerの無償評価版をリクエストして、世界最高のPCB設計ソリューションをお試しください!ご不明な点などございましたら、お問合せフォームにご入力ください。

関連リソース

設計からリリースまで、摩擦なく。

- レビューを適切なバージョンに紐づけ

- 引き継ぎ時の混乱や手戻りを削減

- 調達やリリースのリスクを早期に発見

- 必要に応じて共有しながら、1人でも作業可能

はじめに

Thank you, you are now subscribed to updates.

Platform-based Solutions

Tools

ソリューション

会社情報

採用情報