AMD/Xilinx FPGAとDDRメモリのインターフェース

AMD/Xilinx FPGAとDDRメモリをインターフェースする方法を学びましょう。

イントロ

FPGAへの揮発性DDRメモリのインターフェースは、事前の経験がない場合、初めはかなり難しく感じることがあります。FPGAの固有の柔軟性にもかかわらず、外部DDRメモリのI/Oを任意の空きピンに接続できると思いがちですが、多くの制約を考慮する必要があります。

例えば、特定のDDRメモリピングループをどこに配置するか、バンクを動作させる電圧は何か、必要なクロックは何かとその接続場所、タイミング違反を避ける方法などです。

「回路図レベル」のインターフェースだけでなく、「実世界」のインターフェースについても懸念する必要があります。これには、電源供給、デカップリング、終端、トレースのインピーダンスと長さ、遅延マッチングなどが含まれます。

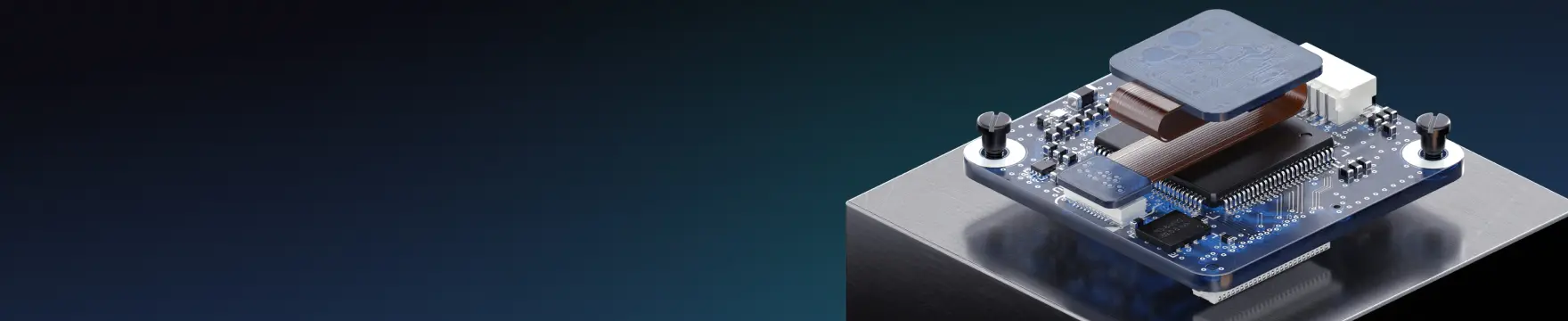

この記事では、システムレベルと回路図の観点からFPGAとDDRメモリのインターフェースについて見ていきます。実用的な例として、DDR2メモリをインターフェースするAMD/Xilinx Spartan-7ベースのオーディオDSP設計(「Xerxes」と名付けられた)を見ていきます。

XerxesオーディオDSPハードウェア(AMD/Xilinx Spartan-7 FPGAとDDR2メモリ)

メモリの種類

使用するメモリの種類は設計に依存します。これは、メモリ容量とメモリ帯域幅の要件、および選択したFPGAの能力によって異なります。

一般的に、ほとんどの現代のFPGAはDDR2およびDDR3メモリ(およびその低電力、低電圧バリアント)とインターフェースできます。もちろん、より高速なDDR4メモリ以上も可能ですが、通常はより高度なFPGAでのみです。

最大可能データレートだけでなく、電圧と電力要件、パッケージタイプ、コスト、および入手可能性も重要です。これらすべては設計段階の早い段階で考慮する必要があります。

DDRメモリ比較(出典:synopsys.com)

メモリタイプを選択する際には、メモリデバイスの速度グレードとFPGA内のメモリコントローラの速度評価にも注意が必要です。メモリまたはコントローラを「ディレート」して、最大帯域幅で動作させないことを選択することで、より多くのタイミングスラックを得ることができます。

典型的なメモリディレーティング表(出典:AMD/Xilinx UG933)

特にAMD/Xilinx FPGAについては、彼らのVivado IDEをダウンロードして、無料のMemory Interface Generator (MIG) IPで遊んでみることをお勧めします。

これにより、使用できるメモリタイプ、速度グレード、互換性のある部品をすぐに確認できます。

Vivado MIG互換メモリ部品の例

なぜXerxesボードにDDR2メモリを選んだのかと聞かれるかもしれません。

かなり古い規格ではありますが、DDR2メモリを使用することで、ボード上に既にある1.8Vレギュレータ(これはFPGAの他の部分を動かすために使用されます)を利用でき、別のレギュレータを追加する必要がなかったからです。

さらに、Xerxes設計は特に高いメモリ帯域幅を必要としていないため、DDR2インターフェースで十分でした。

さらに、帯域幅が低いインターフェースは、PCB、終端、およびタイミングの制約を緩和します。

DDRメモリとFPGAインターフェース

適切なメモリデバイスを選択した後、これをスキーマティックのFPGAに接続する時が来ました。

まず、適切なバンクを選択する必要があります。16ビット幅(またはそれ以下)のデータインターフェースを使用している場合、ほとんどのFPGAでは通常、1つのバンクに収まります。そうでない場合は、メモリインターフェースを複数のバンクに分割する必要があります。

簡単のために、Xerxesボードの場合と同様に、16ビット幅のメモリインターフェースを選択します。DDRメモリ自体と同じ電圧で動作する空いているバンクを選択します(Xerxesの場合、これはDDR2メモリを使用しているため1.8Vのバンク34です)。

1.8V電源から適切なデカップリングを行うFPGAバンク34

AMD/Xilinx FPGAを使用している場合、VivadoおよびMIGツールを使用すると、DDRメモリのピン配置を非常に簡単に取得できます。ツールはそのバンクに適したピン配置を提案するか、またはピンを手動で割り当ててピン配置を検証できます。

Vivado MIGピン配置ツール

ピン配置を手動で設定する場合は、個々のDDRバイトレーンが同じバンクバイト番号を持ち、差動ストローブが差動FPGA DQS対応ピンにあることを確認してください。

ピン配置はPCBのレイアウトとルーティングの段階で調整される可能性があることを覚えておいてください。FPGAの柔軟性のおかげで、PCB設計プロセス中にピンを交換することで、ルーティングを簡素化し、レイヤーの遷移を最小限に抑えることができます。

この例では、単一のバンクから動作しているため、内部VREFを使用する必要があり、これにより最大メモリ帯域幅が制限されます。

さらに、クロッキングに注意する必要があります。理想的には、クロック源は同じバンクにあり、クロッキング対応ピン(または差動クロック源を使用している場合はピン)に接続されているべきです。

最後に、設計とタイミングを検証するためにベンダーツールを使用してください。初期のピン配置が完了したら、回路図でネットクラス、差動ペア、ルールを定義し、色分けを使用してPCB設計の作業を容易にします。

FPGAバンク34 DDR2接続とクロックソース

単一のデバイスについては、DDRメモリコンポーネント上でポイントツーポイントの接続を行うだけで済みます。

アドレス/コマンド/コントロール信号(ACC)には終端が必要ですが、データレートが低い場合はこれを省略できることがよくあります。ただし、差動クロックペアには常に終端を追加します。データバイトレーンは両端で内部的に終端されています。

CKE、ODT、オプションでCS#ラインには4.7kのプルダウン抵抗を配置することを推奨します。

DDR2メモリモジュールの信号および電源接続

最後に、もちろんメモリモジュールには電源が必要です。Xerxesボードの場合、DDR2モジュールはFPGAバンク34と同じ1.8Vレギュレータに接続されています。適切なデカップリングが必要です - データシートやアプリケーションノートで特に指定がない場合の一般的なルールとして、VDDピン2本につき小型(約100nF)キャパシター1個、VDDピン10本につき大型バルクキャパシター1個を使用することを目指してください。

VREFピン電圧は、上記の画像に示されているように、フィルタリングキャパシタを備えたシンプルなポテンシャル分割器を介して生成できます。

まとめ

この記事では、システムレベルおよび回路図レベルの観点から、FPGAベースの設計に外部の不揮発性DDRメモリを組み込むための基本戦略を概説しました。

これらは絶対的な基本事項であり、システム要件に応じて、設計ははるかに複雑になります。特に、より高速なメモリ部品やインターフェースを使用し、複数のモジュールを計画している場合はそうです。

高度なFPGAおよびDDRベースのシステムを設計する際には、Altium Designerのような世界クラスのECADツールに含まれるツールや機能を活用してください。こちらからAltium DesignerおよびAltium 365の無料トライアルを確保してください。