5つの理由:電子設計者が標準JEDECパッケージングを好む理由

Joint Electron Device Engineering Council (JEDEC)は、電子設計とエンジニアリングの世界における基盤的な組織です。1958年以来、マイクロエレクトロニクス産業のためのグローバルスタンダードを開発する中で顕著な存在となっているJEDECの影響は、電子部品がどのように概念化され、作成され、利用されるかに及びます。電子設計とエンジニアリングの専門家にとって、特にパッケージングにおいてJEDECの基準に沿うことは、単なるルールへの遵守を超えて、設計における効率性と卓越性を達成するための戦略的な選択です。

JEDECによって文書化された標準パッケージングは、多くの利点を提供します。互換性の向上から供給チェーンのダイナミクスの改善まで、標準パッケージングは、精度と信頼性が重要な業界において、信頼できる一貫したフレームワークです。この記事では、現代の電子設計における標準JEDECパッケージングの重要な役割を強調し、電子設計者が標準JEDECパッケージングを優先すべき5つの主要な理由を探ります。

1. 互換性と標準化

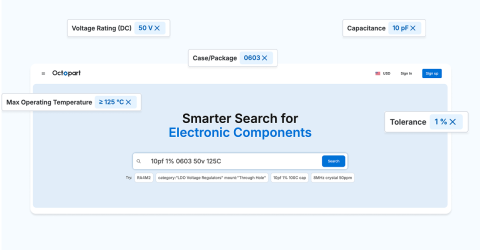

JEDECパッケージングにより、同じパッケージングスタイルで使用される多様なコンポーネントが可能になりました。その結果、多くの半導体メーカーが、最も人気のあるコンポーネントの機能的に互換性のある代替品やピン・フォー・ピンの代替品を作成するようになりました。好みのベンダーから在庫切れの部品を置き換えるためのオペアンプが必要ですか?コンポーネントが同じJEDECパッケージングを使用している限り、異なるベンダーからドロップイン代替品を見つけることができる可能性が高いです。

BOMのクリーニングやBOMラインの代替品を見つけることが非常に簡単になります。すべてのコンポーネントが半導体ベンダー間でピン対ピン互換性を持つわけではありませんが、JEDECパッケージの使用は以下のような一般的な部品の広範囲に普及しています:

- NOR/NAND フラッシュメモリ

- アナログ回路、例えば アンプ

- ラッチ、フリップフロップ など

- 小型低消費電力レギュレータ

2. コスト効率

一部のコンポーネントにおいて、標準JEDECパッケージングはコスト削減にもつながります。これは、今日の競争の激しい環境において重要な考慮事項です。標準パッケージは大量生産され、規模の経済を享受することで、単位あたりのコストを効果的に削減します。このコスト効率は、品質を損なうことなくコストを低く抑えることが戦略的に必要な消費者向け電子製品の大量生産において特に重要です。

標準パッケージングのコスト効率は、コンポーネントの価格を超えて広がります。これは、全体的な設計および開発コストも削減します。標準化された寸法と仕様により、設計者と製造業者は生産プロセスを合理化し、カスタムツーリングの必要性を最小限に抑え、テストおよび検証に費やされる時間とリソースを削減できます。その結果、標準JEDECパッケージングは、品質と手頃な価格のバランスをとる財政的に賢明な選択として浮上します。

3. 実証された性能と信頼性

JEDEC規格は、電子部品の高い性能と信頼性を保証するために業界のベストプラクティスを集約したものです。標準パッケージを選択することで、設計者はその部品が厳格なテストと検証を受けていることを保証します。この高品質基準への準拠は、部品の故障リスクを最小限に抑え、システムの全体的な信頼性を高めます。

この実証された性能は、部品の直接的な機能性だけでなく、長期にわたる信頼性も含まれます。これにより、さまざまな条件下でシステムが長期間にわたって稼働し続けることが保証されます。失敗が財務損失や安全リスクなど、重大な影響を及ぼす可能性がある業界において、JEDEC標準パッケージングによって保証される信頼性は非常に貴重です。

4. 設計と統合の容易さ

標準JEDECパッケージングを選択するもう一つの説得力のある理由は、その設計と統合の容易さです。標準パッケージは、明確に定義された仕様と寸法を備えており、設計プロセスを大幅に簡素化します。設計者は既知のフレームワーク内で作業できるため、部品選択とシステムレイアウトに必要な時間と労力を削減できます。

この使いやすさは、これらのコンポーネントをより大きなシステムに統合する際にも及びます。標準化されたパッケージングは、コンポーネントがシステムの残りの部分と互換性を持つことを保証し、組み立てプロセスを合理化します。設計者にとって、これはトラブルシューティングにかかる時間が少なくなり、イノベーションにもっと時間を割けることを意味し、より高度で効率的な電子ソリューションの創出に集中できるようになります。

5.将来性とアップグレード性

標準JEDECパッケージングは、電子設計の将来性を確保する上で重要な役割を果たします。技術が急速に進化する分野において、システムを容易にアップグレードして適応させる能力は極めて重要です。標準パッケージングは、同じ基準に従う新しいコンポーネントを、広範な変更を加えることなく既存のシステムに統合できることを保証します。この互換性は、アップグレードを単純化するだけでなく、製品の寿命を延ばし、技術が進歩するにつれて製品を関連性があり、機能的に保つことも可能にします。

設計者にとって、この将来性は、創造物が時代遅れになることなく新しいトレンドや技術に適応できることを意味します。これにより、システムが長寿命を念頭に置いて構築される持続可能な電子設計へのアプローチが可能になり、頻繁な交換の必要性を減らし、電子廃棄物を最小限に抑えます。

将来を見据えて

電子設計のダイナミックで厳格な分野において、パッケージングの選択は広範囲にわたる影響を及ぼす可能性があります。私たちが探求したように、標準のJEDECパッケージングは、設計者やエンジニアの核心的なニーズと一致する多くの利点を提供します。標準パッケージングは、互換性と標準化を促進し、供給チェーンの信頼性と可用性を確保し、コスト効率と実証済みの信頼性を提供することで、電子システムの直接的および長期的な要件に対応します。

標準パッケージによる設計と統合の容易さ、将来性の確保、規制遵守の達成という利点は、標準パッケージングをあらゆる電子設計プロジェクトにとって賢明な選択にします。これは、設計プロセスを簡素化し、製品を成功に導く戦略です。

標準のJEDECパッケージングを採用することは、単なるコンプライアンスの決定以上のものです。それは、電子設計における品質、信頼性、および持続可能性へのコミットメントです。業界が進化し続ける中で、これらの標準は間違いなく電子機器の未来を形作る上で重要な役割を果たすでしょう。そのため、標準のJEDECパッケージングを好むことは賢明な慣行です。