SPIラインには必ずしもプルアップ抵抗が必要ではありません

SPIラインにはプルアップ抵抗は必要ありません。プッシュプルバッファの機能に影響を与えずに使用できる特定の場合があります。

SPIバスのラインにはプルアップ抵抗が必要である、または必要であるという一般的な誤解があります。ここで断言しますが、SPIバスにおいてその基本機能であるデジタルデータの送受信を行う上でプルアップ抵抗は必要ありません。

SPIインターフェースのバッファはプッシュプルトポロジーを採用しており、これは(高レベルで)ハイサイドとローサイドのスイッチングMOSFETを含み、基本的にCMOSインバータを形成します。この記事で見ていくように、プルアップ抵抗の存在はプッシュプルバスの機能性に影響を与えません。

それでも、プッシュプルバスにプルアップ抵抗を配置することが理にかなっている場合があり、データシートの中にはコンポーネントメーカーがそれを推奨または要求することがあります。これらの状況とシステムの挙動への影響について見ていきます。これらの状況でプルアップ抵抗の必要性を排除するより複雑な解決策が存在するかもしれませんが、プルアップ抵抗の配置は設計をシンプルに保ち、インターフェースが正しく動作するという保証を提供する解決策となることがあります。

プルアップ抵抗を伴うSPIバスの動作方法

SPIインターフェースのバッファの典型的なモデルを見てみましょう。すべてのSPIバッファには、バスに信号を駆動する高側と低側のスイッチングからなるプッシュプルトポロジーがあり、SPIバス内の各信号(CS、MOSI、MISO、SCLK)にはこのトポロジーがあります。この回路の例を以下に示します。実際のSPIバッファは2つのMOSFETほど単純ではありませんが、一般的な考え方は同じです。

CMOSインバーターをSPIドライバーとして使用。出力はトレース(集中要素として表される)と負荷回路(RC等価モデル)に接続されます。

このトポロジーを使用する主な理由は、バッファ回路の放電容量が出力に比較的高速なエッジレートを提供し、これがバス上のクロック周期よりもはるかに短くなることです。これにより、オープンドレインプロトコル(例:I2C)よりも高速なデータレートが可能になります。

プルアップ抵抗を含むSPIバスは、出力バッファのハイサイドFETと並列に抵抗があるCMOSインバータドライバーと本質的に同じです。さて、ドライバーの各スイッチング状態で何が起こるか、そしてバス上で何が起こるかを見てみましょう。

ロジックHIGH出力

ロジックHIGH出力状態では、NMOSはOFFでPMOSはONです。VDDIOは、接続されたトレースと負荷に電流を供給しています。トレースと負荷のキャパシタンスが充電を始め、負荷で見られる電圧がVDDIOに一致するまで続きます。ここで、PMOSのON抵抗はmOhmのオーダーであり、プルアップ抵抗は1から10 kOhmのオーダーです。明らかに、プルアップ抵抗は非常に大きいため、HIGHロジック出力状態ではPMOSによって実質的にショートサーキットされています。

プルアップ抵抗の存在に関係なく、HIGHロジック状態ではすべての電流がPMOSを通って流れるため、スイッチング特性には影響しません。

ロジックLOW出力

さて、回路がロジックLOW出力状態に切り替わったとしましょう。この状態では、NMOSがONでPMOSがOFFなので、トレースと負荷容量はNMOSを通じてGNDネットに放電しています。PMOSがオフのため、非常に高い抵抗(MOhmのオーダー)として現れ、プルアップ抵抗(1〜10 kOhm)の値よりもはるかに大きくなります。

この場合、プルアップが小さい抵抗であるため、VDDIO/R(pu)の電流値をNMOSに流すことができます。1〜10 kOhmのプルアップ抵抗とVDDIO = 3.3 Vの場合、NMOSへのリーク電流は0.33〜3.3 mAになります。これは、典型的なSPI電流の約50 mAよりもはるかに小さいので、再び、スイッチング特性に影響はないと考えられます。バスのフォールタイムは、負荷とトレースの容量、バッファ回路の出力抵抗インピーダンス、およびNMOSのON状態抵抗によって制限されます。

スイッチングに影響がない場合、なぜプルアップを使用するのか?

明らかに、SPIライン上にプルアップ抵抗を配置しても、バスに信号を駆動する能力には影響しません。したがって、プルアップはデータ伝送とは関係のない何らかの他の機能を果たしているはずで、そうでなければ抵抗は使用されません。

SPIインターフェースの一つまたは複数のラインにプルアップ抵抗を使用する理由は、提案された状況によって異なります。プルアップ抵抗が使用される状況には以下のようなものがあります:

- 周辺機器のCSラインに配置

- ホストデバイスのMISOラインに配置

- 周辺機器のMOSIラインに配置

- 出力ピンの近くのすべてのバスラインに配置

これらの状況での配置の理由は、バスの周辺コンポーネントの一つに論理状態を設定することです。最も一般的な推奨事項は、周辺機器のCSピンにプルアップ抵抗を配置して、それをハイに引き上げることです。周辺機器にアクティブローの有効ピンがある場合、これによりドライバ側のプルがピンをローに設定しない限り、常にピンをハイに引き上げます。

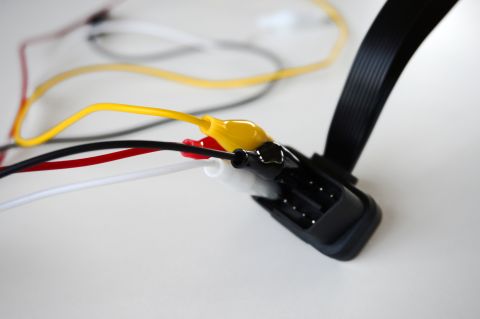

以下にその使用例を示します。PCBレイアウトでは、プルアップ抵抗をこの周辺機器のCSピンの近くに配置します。

SPIバスのCSピンにプルアップ抵抗を配置する典型的な例。

これがなぜ使用されるのでしょうか?指摘されている理由は、システム起動時にCSピンが任意の状態でフローティングしている可能性があり、これによりノイズがバス上のデータを破損するリスクが生じるからです。さらに、ホストデバイスが周辺機器よりも先に起動し、CSピンが意図せず有効になると、ホストが周辺機器内のデータを操作し始める可能性があります。これは、メモリ周辺機器にプルアップを配置する理由として時々引用されます。

現時点で、SCLK(クロック)ラインにプルアップ抵抗を配置するための説得力のある理由は見つかりません。その理由は、他の条件(特にCSラインの状態)が満たされていない限り、クロック信号の存在に関係なく受信ロジック回路はトグルしないからです。いくつかのアプリケーションノートやデータシートでは、さまざまな理由でMISOまたはMOSIのプルアップ抵抗を推奨していますが、これが機能するかどうかをテストすることは簡単で、プロトタイプを作業する際にはいつでも抵抗を取り外すことができます。

電源シーケンシングはより複雑な解決策です

この問題は最もよくシステム起動時のCSピンの状態に関連して指摘されるため、周辺機器とシステムホスト間の電源シーケンスが、起動時のこの問題を防ぐ最良のアプローチだと思います。小規模なシステムでは、複数のレギュレータや必要な電力を通過させることができる電源シーケンサーにデバイス内にスペースがない場合があります。プルアップ抵抗を配置することはよりシンプルな解決策ですが、これらのプルアップ抵抗はインターフェースが正しく機能するために必要ではないことを理解してください。

信頼性の高い電力エレクトロニクスや先進的なデジタルシステムを構築する必要がある場合は、Altium Designer®の完全なPCB設計機能セットと世界クラスのCADツールを使用してください。今日のクロスディシプリナリーな環境でのコラボレーションを実装するために、革新的な企業はAltium 365™プラットフォームを使用して設計データを簡単に共有し、プロジェクトを製造に移行しています。

Altium Designer on Altium 365で可能なことの表面をかすめただけです。今日からAltium Designer + Altium 365の無料トライアルを始めてください.