シミュレーションエンジニア

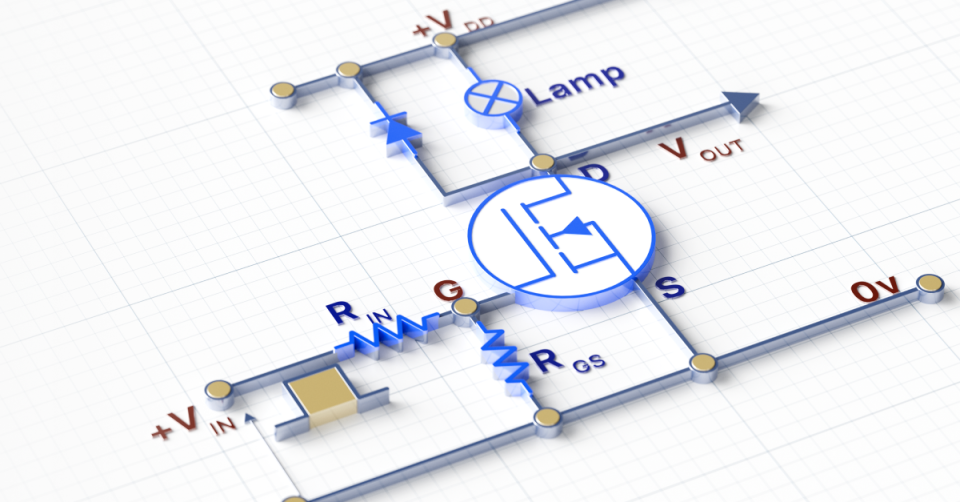

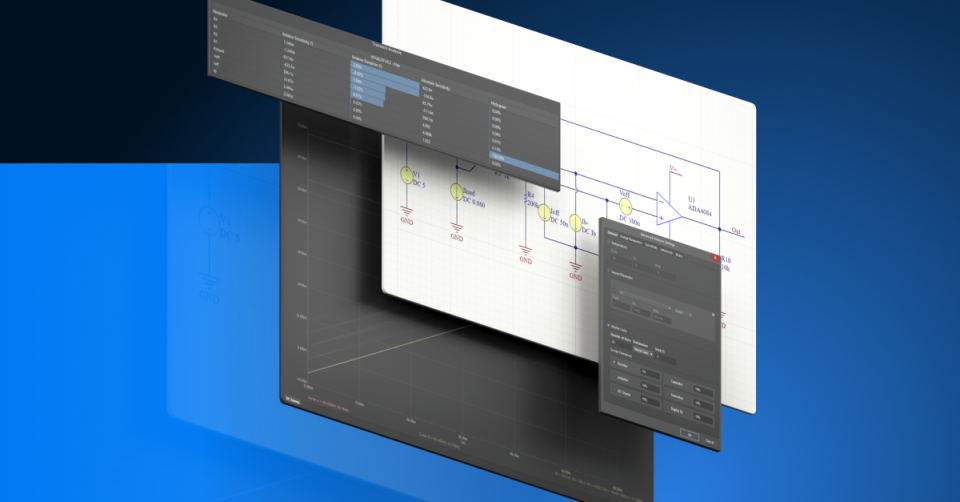

In PCB design, a Simulation Engineer is a specialist who uses testing and simulations to evaluate the performance of products in controlled environments. Their expertise is especially valuable during pre-production and testing phases, where they can help a company make informed decisions about whether to invest in the full-scale development of a product. Simulation Engineers rely on a variety of cutting-edge technologies, including modeling, 3D visualization software, and design testing platforms.

Simulation Engineers are sometimes referred to by other job titles, such as Modeling and Simulation Engineer or Testing Engineer. These titles reflect the broad range of skills and expertise required for success in this role, from modeling and simulation to testing and verification. Overall, Simulation Engineers play a critical role in ensuring that PCB designs meet the necessary performance standards and can help companies make informed decisions about product development.