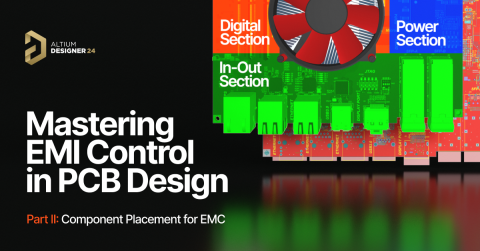

PCB設計者のためのEMIおよびEMCコンプライアンス101

PCB設計および電子製品設計におけるEMIおよびEMCコンプライアンス要件の基本を学びましょう。

EMIとEMCは、PCBデザイナーにとって重要な役割を果たす二つの分野です。PCBデザイナーの仕事は、ノイズ生成が規制限度以下であるように設計を配置することを確実にすることです。当初完全に機能するように設計された多くのシステムが、PCBレイアウトの特定の実践のために規制基準を通過しないことがあります。それから、PCBデザイナーの仕事は、PCBレイアウトを修正して規制基準を通過するようにすることです。

EMC適合性テストの繰り返し、再設計、およびプロトタイプのスピンを防ぐために、デザイナーが取ることができるいくつかの簡単なステップがあります。これらのステップは、PCBレイアウト内の過剰なEMIの発生を減らすのに役立ちます。これらの要因のいくつかは回路レベルで発生し、フロントエンドエンジニアリングおよび回路図のキャプチャで対処されるべきです。しかし、完璧な回路設計であっても、PCBレイアウトが正しくエンジニアリングされていない場合、EMCテストに失敗する可能性があります。このガイドでは、PCBレイアウト内のEMC適合性の失敗につながる可能性のある要因に焦点を当てます。

EMC適合性とは何ですか?

市場に大量に出荷されることを目的としたすべての設計は、運用中に低ノイズ放射を実現する必要があります。放射は、デバイスから離れた場所へ導かれる(ケーブルを通じて)か、またはデバイスから放射されます。これらの放射の両方には、規制当局や業界標準団体によって指定された制限があります。EMCコンプライアンスは、ESDや電子デバイスが過渡現象に耐える能力を中心に展開されます。

以下の表は、世界中のEMC規制と業界EMC標準の下でテストされる内容を大まかに概説しています。このリストは特定の規制を参照することを意図したものではなく、新製品のために実施されるテストの広範な領域と種類のみを示しています。

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

すべての機器がこれらのテストをすべて必要とするわけではありません。例えば、バッテリーのみで動作するデバイスは、電圧の低下と中断のテストに合格する必要はないため、それらの運用要件に基づいて基板を設計する必要はありません。

これらのテストに合格することは規制上の問題であり、規制要件に準拠していることを保証するために電子機器をテストすることを専門とする企業があります。これらのテストは安くはありません。米国では、一回のテストに約10,000ドルの費用がかかることがあります。企業はテストに何度もお金を費やす余裕がないため、テストに出す前に潜在的な失敗を見つけ出す方法を学ばなければなりません。

PCB設計におけるEMC失敗の最も一般的な理由

PCBレイアウトにおけるEMCの失敗は、しばしば少数の理由に帰着され、テストエンジニアの仕事はその失敗の根本原因を追跡することです。これらの問題のいくつかは、レイアウト、ルーティング、またはPCBスタックアップを変更することで簡単に解決できます。

- 不十分な共面グラウンドまたはグラウンドプレーンがない

- 必要のない信号間の隔離のために複数のグラウンドを使用する

- ケーブルやコネクタからの放射または受信

- 一貫したグラウンド参照なしにルーティングからの放射

- グラウンドが取り除かれた高速スイッチング回路からの放射

- 高速プロセッサをサポートするデジタルPDNからのスイッチングノイズ

- 高帯域幅が必要なデジタルPDNからの放射で、フェライトを使用する場合

- 場合によっては、特定の回路のボードレベルシールドが不足している

- 大きな浮遊金属部分からの放射または受信

- 不完全なリターン電流経路により、特に高周波で放射が生じる

- 保護されていないコンポーネントからESD電流を遠ざけることに失敗

- シールド、シャーシ、および/またはアース間の高インピーダンスリターン経路

- ACメイン入力に来るリターン経路のノイズで、PFC(パワーファクター補正)回路

が必要\n上記は網羅的なリストではありませんが、電力および高速デジタル回路、およびケーブリングやエンクロージャーを含むいくつかのケースで一般的なインスタンスを多くカバーしています。過剰なEMIによる多くのEMC失敗は、上記の状況のいくつかの変種が原因です。

あなたの役割がテストエンジニア、特にプリコンプライアンスに取り組む人である場合、あなたの仕事は過剰なEMIの可能性のある全ての原因を探し出して排除することです。これはEMCテストの失敗につながる可能性があるため、非常に重要です。そのため、プリコンプライアンステストのある程度の必要性があります。EMCテストの失敗はほぼ常にシステムの再設計を要求し、これは会社にとって失われた時間とお金を意味します。

上記のリストの中で、私が見つけた問題は、不十分な接地や複数の接続されていない接地の使用がEMCテストの失敗の最も一般的な理由であることです。例えば、密集した2層PCBで何が起こるかを見てみましょう。2層PCBが密集したコンポーネント配置とルーティングを持つ場合、多くの信号が十分な接地を欠き、多くの放射を生じさせます。これは4層PCBに切り替える主な動機の一つです。

Arduino PCBは、コンポーネント密度の限界に近づいているレイアウトの素晴らしい例です。

このPCBレイアウトでは放射線レベルが高い可能性があるため、4層PCBスタックアップを使用することは、他の主要な設計変更を行わずにEMCテストに合格するのに役立つ簡単な方法です。EMI問題はしばしばスタックアップで始まり、システムレベルの問題になることが多いので、プレーン層を追加するような単純な変更が、設計をEMCテストに通すための迅速な方法になることがあります。

EMCコンプライアンスを確保するための設計

EMCコンプライアンスを確保するためにPCBを設計するには、考え方を少し変える必要があります。具体的には、PCBレイアウト内の「ノイズ」とEMC基準で定義される「放射体」と、ノイズがシステムからケーブルを通じて外部にカップリングできる任意の領域との間の一致を見る必要があります。これを早期に認識することで、設計をテストに送る前に潜在的なEMI/EMCエラーを見つけるのに役立ちます。

レイアウトとルーティング

レイアウトと配線は、回路がノイズを低減するために最適に設計されていたとしても、回路のノイズ特性に影響を与えることがあります。これは、ノイズ源と回路間、または回路と自由空間間の寄生結合を通じて発生します。この寄生問題には、単一の記事にまとめるのが難しい複数の側面が関与しています。高いレベルで、寄生を対処するためのレイアウトと配線のアプローチには2つあります:

- 容量 - 回路間の容量性結合を抑制する最も簡単な方法は、グラウンドへのより密接な結合です。

- インダクタンス - コンポーネント間のパスを短くするタイトなレイアウトは、放射を可能にするループインダクタンスを減少させます

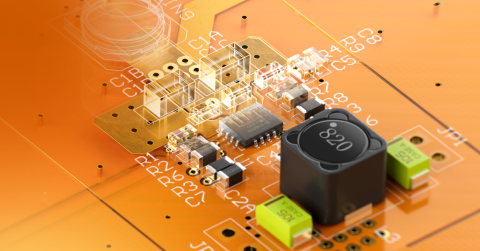

例えば、電力レギュレータでは、これにより回路の出力へのノイズ結合と自由空間へのそれが大幅に減少します。L2上のグラウンド(インダクタの下を含む)でのタイトな配線コンセプトを示す例を以下に示します。

ケーブルの出入り口が過度の伝導放射を持つことが判明した場合でも、配線やレイアウトが最適であっても、共通モードチョークやフィルタ回路を追加する前に調査を試みてください。問題は浮遊グラウンドやエンクロージャーを介した結合による可能性があります。しかし、場合によっては、共通モードチョークは伝導放射のコンプライアンスを確保するのに役立つ単純なコンポーネントであり、ノイズ問題が機能性を妨げない場合には簡単な修正です。

一般的なEMC問題はスタックアップから始まる

最も一般的な放射放射問題のいくつかは、不適切なスタックアップによって生じます。これは、スタックアップがコンポーネント内のノイズを抑制できないため、または悪い配線慣行を引き起こすためであり、これも過度の放射放射を引き起こします。伝導放射の失敗も、主にシステムレベルのグラウンディングが過度の共通モードノイズを生じさせることに関連する不適切なスタックアップからも生じる可能性があります。

低ノイズを確保し、高速/RF信号のインピーダンスを維持し、誘導/容量結合を減少させるスタックアップ設計戦略の例を以下に示します。スタックアップ内で、特定のEMI問題を解決する最も簡単な方法の一つは、グラウンドを利用することです。信号層の間にグラウンドを使用することで、信号グループ間のシールドを提供しつつ、信号線からの意図しない放射放射を減少させます。また、信号遷移時のリターンパスの維持を容易にします。

システムグラウンドを維持するこの戦略は、信号伝播に関連する簡単なEMI問題の多くを解決します。単語「簡単」が「EMCコンプライアンスの失敗を引き起こす可能性が低い」と示唆しているかもしれませんが、これは事実ではありません。高価なテストの失敗は、PCBスタックアップ内のレイヤー配置のような単純なものにまで遡ることができます。

ワイヤレス用のモジュラーアプローチ

製品を完全にモジュラーで市場に出すことは可能ですが、製品を構築するために使用するモジュールが個別にEMCテストに合格している場合に限ります。FCCはモジュラー認証を提供しており、事前に認証されたワイヤレスモジュールを製品で使用できます。これにより、モジュールが既に意図された無線帯域でのみ動作するように認証されているため、デバイスの認証プロセスのRFテスト部分が省略されます。

この認証は、製品に対して他の放射テストを実施する要件を排除するものではありません。しかし、失敗のリスクを減らし、市場投入までの時間を短縮するのに役立ちます。これらのモジュールを避ける他の理由には、特定のフォームファクター目標を達成することや、設計をクローン化またはカスタマイズできない可能性があります。

シールディングは使用すべきか?

私の意見では、PCBレイアウトを正しく行えば、EMCテストに合格するために追加のボードレベルやエンクロージャーレベルのシールドは必要ないはずです。その理由は単純で、コンポーネントと組み立てコストが増加するからです。プロトタイプの場合、このコストはおそらく無視できますが、大量生産では、これらのコストはすぐに積み上がります。したがって、単純にデバイスのシンプルさとコストの観点から、可能であればシールドを避け、設計とレイアウトを完璧にすることが望ましいです。

もちろん例外はあり、デバイスを迅速に展開する必要がある場合など、既存の設計にシールドを追加することが最低コストで最低リスクの進め方になることがあります。時には、完璧なレイアウトでも騒音の多いコンポーネント(例えば、モーター)が存在し、完璧な回路とボードの設計があってもデバイスから出るノイズが多すぎることがあります。EMCテストのゴールラインを越えるための最速の方法のいくつかには:

- コンポーネントレベルのシールド、例えば、SMDやスルーホールシールド缶

- ボードレベルのシールド、例えば、端子メッキ

- エンクロージャマウントフェライトプレート

- 吸収性エラストマー、化合物、およびガスケット

- 大型エンクロージャやキャビネット用の金属ガスケット

- 金属化エンクロージャ

- 接合面を密封する金属テープ

- 吸収性コンフォーマルコーティングの使用

シールドは、問題のあるEMI問題を解決するための魅力的な選択肢かもしれませんが、上記の設計ガイドラインに従えば、追加のシールドコンポーネントや材料が不要であることがわかるかもしれません。

EMC規制

EMIおよびEMCコンプライアンスに関するガイドは、EMC規制の簡単な議論なしには完全ではありません。アメリカ、イギリス、およびヨーロッパには、電子機器のEMI発生およびEMC要件を規制する独自の規制セットがあります。これらの規制は、ノイズ制限の点で互いに似ており、これらのさまざまな市場で販売される特定の製品は、支配的なEMC規制に準拠していなければなりません。EMCコンプライアンス要件のリストはかなり長くなることがありますので、その内容は別の記事で取り上げます。

設計者は、いくつかの理由から、EMCコンプライアンスを推進する規制基準と設計実践を認識しておくべきだと私は考えています。まず、サービスビューロを運営している場合、これによりクライアントにとってはるかに価値のある存在となります。市場への展開ロードマップに存在する規制のハードルをクライアントが乗り越えるのを助けるために必要なスキルを持っていることになります。もう一つの理由は、EMCテストエンジニアとより深く連携し、共通のレベルで彼らと話すことができるようになることです。

EMCコンプライアンスにおける一般的な課題について学んだ今、PCB設計に必要な完全なツールセットをAltium Designerで使用することを確認してください。Altium Designerは、SI、PI、EMI/EMCシミュレーションのための最先端アプリケーションとの統合も提供する業界をリードするCADプラットフォームです。設計が完了し、製造業者にファイルをリリースしたい場合、Altium 365プラットフォームを使えば、プロジェクトの共有やコラボレーションが簡単になります。

Altium DesignerとAltium 365で可能なことの表面をかすめただけです。今日からAltium Designer + Altium 365の無料トライアルを始めてください。