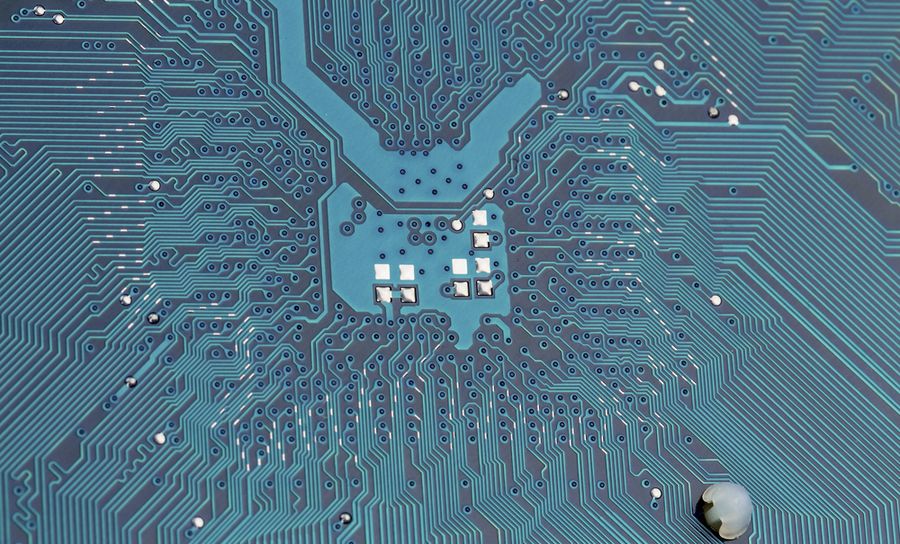

PCB配線

PCBの配線では、コンポーネント間の銅箔の接続を行います。最適な配線を行うことで、シグナルインテグリティー、低クロストークと低EMIを確保できます。PCBの配線や配線ルール、信号規格の遵守に最適なPCBレイアウト用ソフトウェアについては、当社のリソースライブラリをご覧ください。

Filter

見つかりました

Sort by