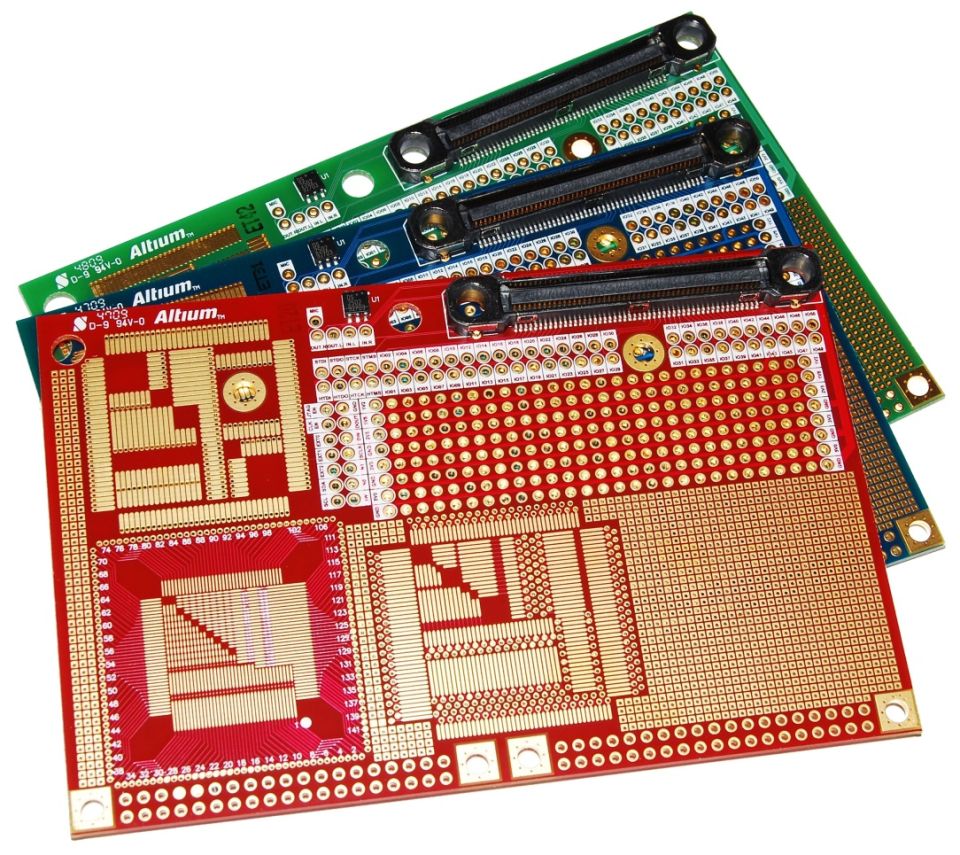

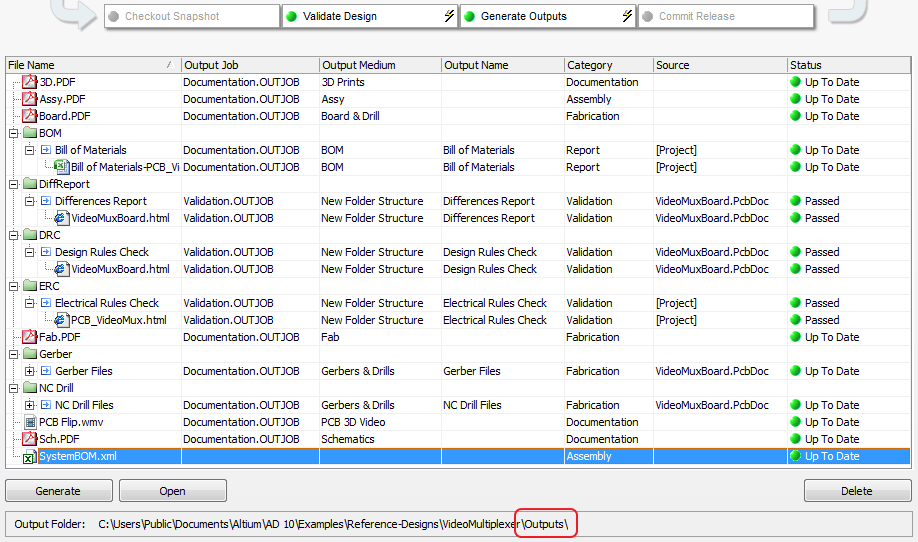

Systems and Product Design

Integrate multidisciplinary systems seamlessly, from conceptualization to final product design, for enhanced performance and reduced development time.

Filter

見つかりました

Sort by