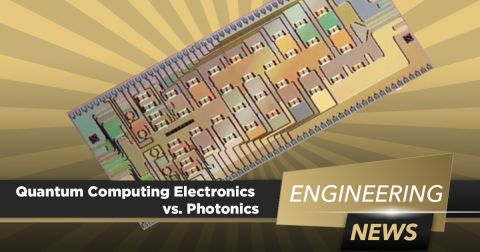

アンチパッド直径、クロストーク、およびIBMの結果 IPC APEX EXPO 2021から

インターレイヤークロストークはアンチパッドの直径から始まり、IBMの結果は、バックドリルされたPTHのアンチパッド直径が信号の整合性にどのように影響するかを理解するのに役立ちます。

最近、IBMをPCB業界の主要な力として考えることはおそらくないでしょう。IBMはクラウドへの大きな推進を行っていますが、電子業界からはあまり評価を受けていません。しかし、メインフレーム、サーバー、Watson、AI能力で知られるこの会社は、IPC APEX 2021で発表された最近の結果により、高速設計コミュニティ内で波を起こしています。

IBMの研究者3人のチームによって発表された論文は、バックドリルされたPTHビアを使用した高密度設計における層間クロストークを減らす方法を探っています。この論文は非常に興味深いもので、バックドリルされたPTHビアの設計の2つの側面を調査しており、それらは直感的にクロストークを減らすことと結びつけられないかもしれません。しかし、高速インターコネクト間の非常に低いスペーシングを持つ高密度設計では、クロストークを含む信号整合性の問題を減らすために、あらゆる場所を調べる必要があります。

アンチパッドとその信号整合性への影響を見るとき、その結果は非常に興味深いものです。これを念頭に置いて、これらの興味深い結果を見て、今後の設計実践にどのように影響を与えるかを探ってみましょう。

層間クロストークとは何か?

IBMの論文の本題に入る前に、高速PCBにおける層間クロストークを定義することが重要です。高速PCBの2つの層の間でなぜクロストークが発生するのか疑問に思うかもしれません。高速PCBの信号層の間には通常、層間のクロストークを防ぐためにグラウンドプレーンを配置するのではないですか?確かに、信号層の間にグラウンドプレーンを配置することで隔離が提供されるのは事実ですが、可能なすべての信号層のペアの間にグラウンドプレーンを配置するのは時に難しいことがあります。高い層数の設計では、高速信号の密集したルーティングもサポートしなければならず、すべての信号層の間にグラウンドプレーンを配置するという贅沢は常に許されるわけではありません。

層間クロストークの登場です。隣接する層にトレースが配置されると、導体間の結合によりトレース間でクロストークが発生する可能性があります。これには、隣接する層上の制御インピーダンスのブロードサイド結合トレース間のクロストークも含まれます。制御インピーダンストレースに対する一般的な推奨事項は、それらを直交にルーティングすることで、これにより誘導性クロストークが排除されるとされていますが、これが常にルーティングの解決可能性の観点から実用的であるわけではありません。

ブロードサイド-エッジ結合

個人的には、ストリップライン上での直交ルーティングは避け、横方向の分離(エッジ結合)や異なる層での分離を選択します。非常に高密度な設計では、隣接する層上でストリップラインを使用せざるを得ない場合、トレース間にはブロードサイドまたはブロードサイドエッジ結合が発生します。これは単線トレースと差動ペアの両方で発生し、高速デジタルルーティングでは差動ペアを扱うことになることに注意してください。

ブロードサイドエッジ結合された差動ペアでは、隣接層のペア間に特定のピッチがあり、逆方向の層間クロストークがゼロになります。実際にはクロストークの強度が完全にゼロになるわけではありませんが、クロストークの強度を-60 dB以下にすることは確かに可能です。差動ペアでは、攻撃側ペアの場が被害ペアの断面に完全に平行になるため、ファラデーの法則により層間誘導性差動クロストークがゼロになります。

ミスレジストレーション

製造公差により、差動ペア間のピッチは設計値と完全には一致せず、層間に若干のずれが生じます。これをミスレジストレーションと呼び、被害ペアでわずかなクロストークが発生する原因となります。このミスレジストレーションは最大で5ミルに達することがあり、これはIBMの研究で調査された値の一つです。

SamtecのScott McMorrowによる優れたプレゼンテーションがあり、差動ペア間の不整合が層間クロストークに与える影響を示しています。彼のプレゼンテーションから重要な結果を以下に示します。これは、ペア間ピッチが前方クロストークにどのように影響するかをうまく示しています。

IBMの論文の結果

ここで、IBMの層間クロストークに関する研究について詳しく見ていきましょう。彼らは層間クロストークを2つの側面から検討しました:層のミスレジストレーションとPTHビアのアンチパッド直径です。自然とミスレジストレーションの削減が層間クロストークに最も大きな影響を与えると考えられますが、実際にはアンチパッド直径の調整がミスレジストレーションの削減よりも層間クロストークを減少させる効果が大きいことがわかりました。

彼らの論文の結果を全て繰り返すことなく、重要な信号整合性の結果を簡単にまとめます:

層間クロストークと信頼性 vs. ミスレジストレーション

ミスレジストレーションが5ミルから3ミルに減少したとき、被害線上の層間クロストークの強度が減少し、これは上記のMcMorrowの結果と一致しています。この結果の重要な点は、それが普遍的であることです:より厳しい公差は、より小さなミスレジストレーションとPCBレイアウト全体での低いクロストークにつながります。

チームが見つけたより驚くべき結果は、同じタイプのクロストークに対する変化するアンチパッド直径の効果でした。

アンチパッド直径

バックドリルされたPTHビアを介して層間移行を行うトレースの場合、アンチパッド直径もまた、結合された相互接続間の層間クロストークに影響を与えることがわかりました。スルーホールビア周りのアンチパッドは、ビアと近くのトレースの周りの寄生要素を変更し、わずかなインピーダンス不一致を生じさせ、損失が蓄積することが既に知られています。IBMの論文では、10ミル直径のPTHでアンチパッド直径を30ミルから28ミルに減少させることも、層間クロストークの減少をもたらしました。これはクロストークを減少させるためのシンプルな設計変更の一例ですが、正確なバックドリリングを伴うPTH周りの厳密な公差に依存しており、すべての製造業者が対応できるわけではありません。

要約

IBMの論文で示された結果は重要であり、それは重要な信号整合性問題と小さなスケールでの製造公差との間の関連を示しているからです。先進的な設計がよりコンパクトになるにつれて、これらの調査が増えることで、製造公差が信号および電力整合性に与える影響を明らかにするのに役立ちます。層間クロストークは新しい問題ではありません。二重ストリップラインにおける層間クロストークを減少させるための良いレビューといくつかの代替ルーティング戦略については、以下の2013年の論文で見つけることができます:

ここAltiumでは、アンチパッド、クロストーク、高速設計における信号整合性のようなインターコネクト設計の最新の発展について、皆さんに情報を提供することを目指しています。電子機器のパッケージングの境界を押し広げ続ける電子業界では、Altium Designer®およびAltium 365™プラットフォームを使用して、最高品質の設計を構築するために必要なすべてのツールを手に入れることができます。エンジニアリングと技術のアップデートについては、ブログを引き続きご覧ください。