RF電源用の多相バックコンバータの設計

RF電源のレギュレータ段階で多相バックコンバータを検討してください。エンベロープトラッキングと併用することで、高効率な電力供給と伝送を実現できます。

つい昨日のように感じますが、私たちが将来の5G展開について話していたところ、初期の5Gネットワークがすでにアメリカ、中国、韓国で実現し始めています。5Gシステムは、基地局や送信機器、さらにはハンドセット、自動車、中継器、IoT製品の設計アプローチを変えています。5Gのさらなる展開は、基地局の革新と送信機器を小規模なローカルセルに拡大することなしには実現できません。これにより、サービスをユーザーに提供できます。

現場で見つかる基地局機器のセットの中で、RF電源とアンプは信号伝送において中心的な役割を果たし、これらのシステムでのシグナリングを高効率でサポートするように設計されている必要があります。残念ながら、以前の世代のSi、SiC、GaAsパワーMOSFET製品は、アクティブデバイスから十分な熱を逃がしてデバイスを冷却状態に保つことが一般的にできません。2019年の夏にこの加熱問題の一種を目の当たりにしました。新しいスマートフォンの5Gモデムが過熱でシャットダウンしていました。基地局でも同様の問題が発生します。

通常、電力増幅段は運用中に熱を発生させるため、DC電源で駆動される場合には、ヒートシンクやファンのような部品を使用して冷却する必要があります。RF送信システムでは、ヒートシンク、大型の筐体、ファン、その他の冷却装置に多くのスペースを割く必要があります。より小さなRF電源のフットプリントと高効率を実現するには、いくつかのシンプルだが重要なステップがあります:

- SiC上のGaN FETのような新しい半導体デバイスの使用

- 電源および増幅器のための代替レギュレータトポロジー、例えばエンベロープトラッキングを備えたマルチフェーズバックコンバータの使用

この記事では、主に2番目のポイント、特にRF電源および増幅器における高い電力変換効率を可能にするレギュレータトポロジー、マルチフェーズバックコンバータに焦点を当てます。この設計を通じて、このコンバータのスイッチング要素としてGaN MOSFETを使用した例を示し、このタイプのコンバータがRFシステムの電源にどのように統合されるかを説明します。このタイプの電源設計は、周波数変調信号を持つRFエミッタに安定した電力を供給することを目的としています。

エンベロープトラッキング電源

RFパワーアンプに直流電力を供給する好ましい方法は、エンベロープトラッキング電源を使用することです。この特定のタイプの電源を設計する方法の詳細には触れませんが、それは別の記事のために残しておきます。エンベロープトラッキングを使用する主な利点は、運用中の熱の放散が少ないことです。エンベロープトラッキング電源は、アンプを通じて引き出される変調信号の重ね合わせられた振幅エンベロープを追跡します。この方法では、アンプに供給される電力は、入力信号と同じ瞬間に増加または減少するため、内部FETがオフ状態に近づいているときに熱として放散される電力が少なくなります。

これらのシステムは、エンベロープトラッキングを使用しない同様の電力システムと比較して、平均電力比(PAPR)が高くなる傾向があります。エンベロープトラッキング電源は、線形アンプ、スイッチングコンバーター、および線形アシストスイッチングを備えたコンバーターで使用されてきました。アンプでの熱として失われる電力を減らす目的は、高効率を確保することです。RF電源で実装された高帯域幅のエンベロープトラッキングは、低ノイズでの正確な調整を要求します。これをデジタルシステムと対比すると、スイッチングノイズは電力バス上の過渡現象よりもはるかに重要ではありません。

このエンベロープトラッキングRF電源アプリケーションでは、マルチフェーズバックコンバーターを使用したいと考えています。このタイプのバックコンバーターは、標準的なLC配置(標準的なバックコンバーター回路で見つかるもの)を駆動するために、強制的な位相遅延を持つ複数の駆動段を使用します。このタイプのバックコンバーターを使用したい理由は3つあります:

- 低デューティサイクルで動作させ、定義された位相関係を設定することにより、出力インダクターの電流はより高いスイッチング周波数を見ることになり、低ノイズに有利です。

- #1のため、より高い組み合わせスイッチング周波数で駆動することで、物理的に小さいインダクターを使用できます。

- 出力インダクターを駆動する等価スイッチング周波数が高くても、個々のスイッチング段階を低い周波数で駆動することができます。

- 適切なインダクターや位相遅延ドライバーを使用することで、ゼロ電圧スイッチング(ZVS)を実装でき、ソフトスイッチング中の損失をさらに削減できます。

マルチフェーズバックコンバーター設計

以下のブロック図は、多相電力コンバータの基本設計概念とトポロジーを高いレベルで示しています。位相制御は、並列に配置された複数のスイッチング段階全体に実装されます。これらは出力バスを共有し、出力はローパスフィルタを通してリップルを減少させます。

下の画像は、多相コンバータのスイッチングセクションの一つの例示的な回路図を示しています。スイッチング段階は、これらのシステムの中で最も複雑な部分です。各セクションからの出力(各セクションのL1から)は、出力フィルタに接続する出力ポートに収束する長いバスに並列に接続します。πフィルタは、標準的な(単相)バックコンバータと同じ機能を実行する受動的エンベロープトラッキングを実装するための優れた選択です(ローパス差動モードフィルタ)。

この設計は、適切な高周波PWMドライバーを使用する限り、ZVSを用いて約100 MHzのスイッチング周波数で動作させることが考えられます。上に示された4次の出力フィルターは、必要な帯域幅内でのエンベロープ追跡を提供します。下のタイミング図は、高側フライングキャパシタ(VCa)における電圧制御が、Vin/2からVinまでの出力レベルで、0.5 < D < 1.0の範囲でどのように実装されているかを示しています。全出力電流にはまだいくらかのリップルが含まれていますが、高側および低側のMOSFETにおけるスイッチング周波数と比較して4倍の周波数です。

フライングキャパシタ(CaおよびCb)はここで重要な役割を果たし、典型的な単相バックコンバーターと同じ機能を持っています:MOSFETアレイが切り替わるたびに周期的に充電および放電し、出力インダクタを通じて電力を供給します。上のグラフから導き出せる一つの重要な結論を指摘したいと思いますが、これは以前には明らかではなかったかもしれません:

多相コンバータは、N倍の周波数で駆動される単相コンバータのように振る舞うか、またはN倍の出力インダクタンスを持つように振る舞います。

これがスイッチングコンバータの主な利点です。エンベロープトラッキングと低RONのGaN FETを組み合わせることで、この電源からアンプに供給される電力はノイズが大幅に少なくなりますが、フットプリントは小さく、冷却要求も軽減されます。次に、各フェーズのGaN FETと出力インダクタを選択する必要があります。

インダクタの選択

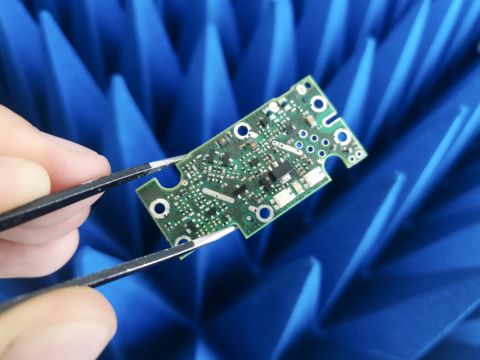

このタイプのシステムを実装するために、次のタスクは、設計で使用されるFETとインダクタ(高側と低側にL1とマークされている)を選択することです。これらのインダクタは、トランジスタのドレイン-ソース電圧値がドライバーによって切り替えられるときにZVSを駆動するために重要です。このタイプのアプリケーションでは、GaN FETとMMICが、低いRON値と高い熱伝導率のため、電力システムのスイッチング要素として使用するのに最適です。これにより、熱がPCB基板や近くのヒートシンクに放出されます。

明らかではないかもしれませんが、このシステムのインダクタはZVSに到達するために適切なサイズでなければなりません。このスイッチング条件は、ピークからピークまでのリップル電流が平均電流の値の2倍以上になるようにL1の適切な値を選択することによって達成されます。通常、ZVSを実装するには、出力電流がZVSサイクル間で動的に制限される複雑な制御回路を使用する必要があります。

次に、望ましいデューティサイクル範囲に対応するように設計されるべきインダクタL1について説明します。Nフェーズ三レベルコンバーターの場合、高側スイッチQ1およびQ2でZVSに到達するために必要なL1の最大値は、負荷抵抗RL、デューティサイクルD、および等価スイッチング周波数fs,eqによって決まります:

これらのコンバーターのデューティサイクルは0.1から0.9までの範囲で変動することができます。L1はDの最大値または最小値で決定されるべきです。このコンバーターはパワーアンプリファイアの入力に接続され、アンプが駆動信号を受け取ると低インピーダンスに落ちます。

最終的に、上記の方程式でのf項(等価周波数)は以下のように示されます。ここで、N = 2の場合、上のグラフから期待されるように、駆動周波数の4倍になることに注意してください。

FET選択

高周波設計において、ここでの例である4G LTEやそれ以上の動作周波数の場合、電力システムはSiパワーMOSFETを超える必要があります。GaN FETは、Siが使用できない高周波数でのON状態損失が少ないため、現時点で理想的なデバイスです。最も近い対応物はGaAsとSiGeですが、これらの材料プラットフォームは、高効率の電力変換が必要なmmWave周波数でまだ性能不足です。

このタイプのRF電源供給にSi MOSFETを超えるものが欲しいいくつかの理由があります:

- ゲート容量の低下

- 反転層とバルク層の高移動度

- デバイスの高温度限界

- 高い耐圧界

- 高い熱伝導率

- 低容量

- 駆動時の深い飽和

いくつかの例としてOctopartの検索結果を見てみましょう。FETを選択したら、任意の駆動信号でシミュレーションを見て、このレギュレータ設計の電力変換効率を決定できます。スイッチングFETの実際のモデルが利用可能であれば、SPICEシミュレーションでこれを行うことができます。ここでは、負荷に供給される時間平均出力電力(出力電圧Voを使用して)と、さまざまなデューティサイクルに対するフライングキャパシタの電圧を比較したいと思います。

ここでのもう一つの主要な回路の課題は、FETアレイを直列に接続することです。過去に並列MOSFETアレイについて議論しましたが、アレイ出力に少しの抵抗を配線しないと振動することが知られています。実際には、直列FETは特にスイッチングセクションに高入力電圧がある場合、電力システムで扱うのがより難しいです。直列配置では、設計全体にわたって電圧が均等に分配されることを目指しますが、これはゲート電圧に依存して接合抵抗が非線形であるため、かなり難しいです。一般に、直列アレイの最初のFETが最も多くの電圧を消散させるので、最初に故障します。この問題については、今後の記事でさらに詳しく見ていきますが、CMOSバッファの構造が示すように、これは統合回路設計における根本的な問題です。

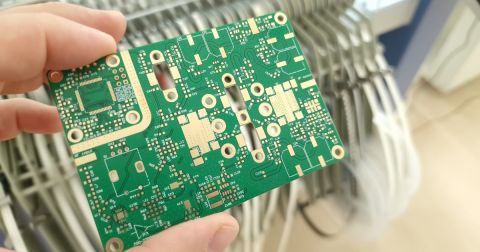

多相バックコンバータのレイアウトのヒント

レイアウトで考えるべき重要な点は、隔離、FETアレイからの熱の放散、および上述のようにアレイ内のFET間で電圧降下を均等に分配することです。

- 絶縁: ボードを密接にルーティングして低インダクタンスを確保することは、設計の下流から受ける過剰なEMIやノイズを防ぐための最初のステップです。近くのグラウンドプレーンは低インダクタンスルーティングを確保し、ある程度のシールドを提供します。

- 配置: FETの直列配置と、近くにPWMコントローラーを配置する必要があることを考えると、設計から引き出されるRFパワーが設計の入力側に戻らないように、すべてを直線的に配置することをお勧めします。

- 熱放散: RF電源に必要な高度なFETは多くの熱を発散しますが、その熱はどこかに行かなければなりません。近くのプレーンは熱がFETから伝導していくための良い選択肢です。ボードとエンクロージャーの間に熱インターフェース材料を使用することも、供給される熱を取り除くのに役立ちます。

現代の電子機器に最適な回路設計およびPCBレイアウトユーティリティをお探しの場合、Altium Designer®の完全なPCB設計ツールセットを使用してください。設計における電力の整合性とEMIを評価する必要がある場合、Altium DesignerのユーザーはEDB Exporter拡張機能を使用して設計をAnsysフィールドソルバーにインポートし、さまざまなSI/PIシミュレーションを実行できます。設計が完了し、製造業者にファイルをリリースしたい場合、Altium 365™プラットフォームを使用すると、プロジェクトの共有やコラボレーションが簡単になります。

Altium DesignerとAltium 365で可能なことの表面をかすめただけです。今すぐAltium Designer + Altium 365の無料トライアルを開始してください。