フレックスPCBにおけるハッチドグラウンドプレーンインピーダンスシミュレーション

フレックスPCBも高速PCBになることができますが、ハッチングされたグラウンドプレーンが必要です。ハッチングされたグラウンドプレーン上でのインピーダンスを決定するためのいくつかのヒントをここに示します。

フレキシブルPCBとリジッドフレックスPCBは、制御インピーダンスを必要とする高速信号を伝送することができます。フレックスPCBに制御インピーダンスを実装することは、いくつかの理由から簡単な作業ではありません。制御インピーダンスのルートを選択し、メーカーがインピーダンスをテストしてスタックアップを調整する場合、これを行う自由がほとんどないことがあります。これは、フレックス層の厚さを厚すぎるか薄すぎるかにする可能性があるためです。制御された誘電体のルートに進むと、グラウンドプレーンの構造がインピーダンスのための典型的なモデルを無効にするため、適切なインピーダンスを決定することが非常に困難です。

残念ながら、これはフレックスPCB内の単一トレースと差動ペアのインピーダンスを決定するために、いくつかのシミュレーションやテストデータを使用する必要があることを意味します。すべてのメーカーがこのデータを提供できるわけではなく、また、このデータを持っていても、公開することがないかもしれません。差動ペアに関しては、インターコネクトに沿ったインピーダンスを決定する重要な要因も間隔になります。

この記事では、Lukas Henkelの研究に触発されて、ハッチドグラウンドプレーン上のトレースインピーダンスの決定に使用できるシミュレーション結果とワークフローの簡単なセットを紹介します。

ハッチドグラウンドプレーンインピーダンスシミュレーションの動機

最近、私たちはLukas Henkelとのフォローアップインタビューを行いました。そこでは、オープンソースラップトッププロジェクトにおける彼の進捗について話し合いました。このプロジェクトは、オープンソースのラップトップ用のマザーボードと周辺機器を作成することを含んでおり、周辺機器の一つには、ディスプレイの上部に設置されるウェブカメラがあります。もっと知りたい方は、私たちのインタビュークリップをご覧いただくか、YouTubeで全エピソードをご覧ください。

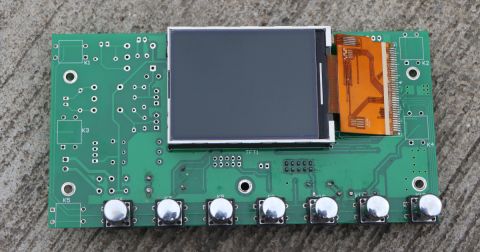

このクリップでウェブカメラの設計部分を参照すると、ウェブカメラはフレックスPCBを使用してマザーボードに接続されます。カメラからCPUへデータをルーティングするためには、高速シリアルリンクが必要です。これには、MIPI CSI-2、4つの平行レーンとソース同期差動クロックを使用してシリアルデータを送信する高速差動インターフェースの使用が必要です。合計で、これによりカメラとマザーボードの間に最大5つの差動ペアが走ります。

4つのデータレーンとソース同期クロックレーンを介したCSI-2のルーティング。各差動ペア内の両トレースには長さ調整が必要であり、差動ペアはこのグループ内でマッチングされなければなりません。

差動インターフェースであるため、インピーダンス制御を100オームに要求する差動ペアを使用してください。リジッドPCBでは、これはかなり簡単です。レイヤースタックマネージャーとAltium Designerまたは他のシミュレーターを使用して、スタックアップの断面に基づいて損失のないインピーダンスをすぐに取得します。フレックスPCBでは、これはそう簡単ではありません。なぜなら、フレックスPCBはハッチングされたグラウンドプレーンを使用するからです。さて、この理由を示す理論を簡単に見てみましょう。その後、Lukasのフレックスリボンのシミュレーション結果を示し、差動インピーダンスと差動Sパラメータの詳細を説明します。

フィルファクターはインピーダンスを決定する重要なパラメータです

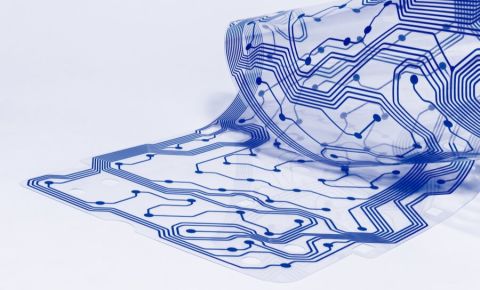

ハッチングされたグラウンドプレーンを持つフレックスPCBの銅インターコネクトのインピーダンスを評価する際、インターコネクトで何が起こっているかを理解するために使用できるツールの1つが入力インピーダンスです。ハッチングされたグラウンドプレーンの構造を見ると、ハッチには銅が取り除かれている領域があり、通常は正方形またはダイヤモンド形をしており、その領域はハッチングされたグラウンドプレーンを構成する繰り返しエリア要素のいくつかの割合として定義できます。この割合を「フィルファクター」と呼んでいますが、以下の画像に示すように定義できます。

さて、上記の構造の異なる領域を越えてトレースをルーティングしましょう。トレースの一部は固体銅の上を通り、他の部分は銅が取り除かれた領域をルーティングします。トレースの近くの接地の存在の変化は、インピーダンスに影響を与え、これによりこれらのルート上の信号の整合性に影響します。トレースの長さに沿って、トレースと銅の距離の関数となる高インピーダンスと低インピーダンスの変動が予想されます。

ルートの長さに沿ってインピーダンスの変動があるため、この構造は周期的にカスケードされた伝送線です。このタイプの構造を具体的に説明している良いリソースを研究文献で見たことがありませんが、この記事でそれに言及しています。いずれにせよ、各セクションには入力インピーダンスがあり、次の伝送線セクションの観点から記述することができます:

簡単に言うと、各伝送線路セクションの特性インピーダンスを知っていれば、誘導計算によってSパラメータの妥当な推定値を得ることができ、PythonスクリプトやExcelで簡単に行うことができます。例えば、銅の上とハッチ領域のインピーダンスを知っている場合、上記の方程式を繰り返し使用して、入力ポートでのリターンロス(S11)を推定することが考えられます。

この方法は、固定平面を仮定してから何らかの補正係数を適用するよりも正確だと私は主張しますが、これはさらなる研究の対象だと思います。いずれにせよ、ハッチドグラウンドプレーン上での単線または差動インピーダンスの推定値を得たら、最終的にはこれを検証する必要があり、それには3Dシミュレーションが必要です。

ハッチドグラウンドプレーンの3Dシミュレーション

ハッチドグラウンドプレーン上のインターコネクトの性能をより完全に検証するために、以下に示すようにLukas Henkelがオープンソースのラップトップ用に提供したフレックスリボンを使用します。以下の画像は、フレックスリボンと2つの領域でのトレースルーティング、および各領域のトレースグループを示す3Dビューを示しています。

レイヤー1:

レイヤー 2:

まず、Simbeorのコンプライアンスアナライザーを使用して、トレース断面に基づいてインピーダンスを取得し、各セクションの特性インピーダンスの値をいくつか取得します。2つの領域が調査され比較されました。カメラコネクタから直接来る直線領域では、単線のインピーダンスの変動が非常に小さいように見えます。インピーダンスは直線上で30-40オームの範囲で変動します。フレックスケーブルの曲がった領域では、インピーダンスの変動がはるかに大きく、特性インピーダンスは30-60オームの範囲です。

幅広のライン幅(W/H = 4)は、銅上に非常に低い奇数モードインピーダンスの領域を作り出しますが、銅の間の領域は50オームの目標にはるかに近いです。正確な変動は約28-62オーム、または平均して45オームの奇数モードインピーダンスのようです。差動インピーダンスは約78オームで、多少の変動があります。

直線領域:

曲がった領域:

既に見ている通り、リンクに沿って大きなインピーダンスの偏差がいくつかありますが、その長さは小さいので、このリンクに沿っていくつかのモード変換が発生すると予想されます。このリンクの完全なSパラメータ行列は、損失とモード変換を教えてくれます、そして結果は次のセクションに示されます。

CSI-2 Sパラメータ結果

さて、インピーダンスが制御されているCSI-2リンクのSパラメータを見てみましょう。上で示された断面インピーダンス値のみに基づいて、インターコネクトに沿った実際のリターンロスがどのようになるかは非常に不明確です。したがって、非常に高い周波数までのリターンロスを決定するために、このジオメトリからSパラメータシミュレーションを実行します。下の画像は、上で強調表示されたCSI-2レーンの結果を示しています。

リターンロスはCSI-2リンクに必要な限界内で許容され、トレースの幅のおかげでチャネル帯域内では挿入損失が非常に低いですが、帯域限界を超えると急激に減衰します。ここでの問題の一つはモード変換、特にSCD21(右下のグラフ)については、ハッチングされたグランドプレーンの不連続な性質を考えると予想されるものです。このリンクには多くのモード変換があり、MIPI C-PHYの限界に対してチェックする必要があります。

リターンロスと挿入損失の結果を改善したい場合は、差動リンクの充填率と間隔を調整する必要があります。その後、再度シミュレーションを行い、Sパラメータが改善されたかどうかを確認する必要があります。詳細については、以下のワークフローセクションを参照してください。

結果とワークフローの要約

私たちの目的では、PCB上のトレースルーティングを見ているだけなので、この結果は受け入れられます。実際には、フルインターコネクトのSパラメータは、コネクタに入るケーブルインターフェースでのインピーダンスミスマッチに依存します。上に示されているものを超えてシミュレーションを拡張するには、次のことを行う必要があります:

- このリンクのSパラメータのタッチストーンファイルをエクスポートします。

- 両端のコネクタ用のタッチストーンファイルを取得します。

- CPUとカメラチップに繋がるリンクのタッチストーンファイルを取得します。

- これらをすべて線形ネットワークモデルに追加します。

- 全体のカスケードネットワークのSパラメータを決定します。

- これらの結果に基づいて、CSI-2差動ペアの下にあるハッチングされたグラウンドの充填率を調整する必要があるかもしれません。

- 繰り返して反復します.

上記のプロセスは、CSI-2レーンのトレースインピーダンスを決定するために実施されるワークフローを示しています。ハッチングされたグラウンドプレーン上でのトレースインピーダンスの予測に使用できる正確な解析結果が不足しているため、充填率に基づく推定から始めて、適切なトレースインピーダンスを得るためにいくつかのバリエーションを反復する必要があります。以下のワークフローを提案します:

- 提案されたハッチングデザインから始めて、充填率を計算します。

- バリエーションとして使用するために、2つの追加の充填率を計算します。

- これらのバリエーションを持つ小さなテストボードを設計し、それぞれでSパラメータをシミュレートします。

- Sパラメータの結果を調査し、最適な充填率を選択します。

- 差動ペアの場合、結果を調査し、差動インピーダンスを増減させるために間隔を調整する必要があるかどうかを決定します。

- 修正された差動リンクをシミュレートし、Sパラメータをチェックします。

- 繰り返して反復します。

これら3つのシミュレーション、および差動ペア間隔の調整に基づく可能性のある第4のシミュレーションを使用して、約8時間のシミュレーション時間でわずか4回のシミュレーションで使用可能なインターコネクト設計に到達することができます。これは1日で完了するのに十分な速さです。

フレックスPCB内のハッチングされたグラウンドプレーン上での単終端および差動リンクの性能についてさらに洞察を提供するために、より大きなジオメトリ研究を行う予定です。これには、多くのフィルファクターパラメータを変化させ、単終端および差動インピーダンスの最も効果的な推定器となる幾何学的パラメータを決定することが含まれます。このブログシリーズのさらなる更新情報にご注目ください。

信頼性の高い電力エレクトロニクスを構築する必要がある場合でも、高度なデジタルシステムを使用する場合でも、Altium Designer®の完全なPCB設計機能セットと世界クラスのCADツールを使用してください。今日のクロスディシプリナリーな環境でのコラボレーションを実装するために、革新的な企業はAltium 365™プラットフォームを使用して設計データを簡単に共有し、プロジェクトを製造に移行しています。

Altium DesignerとAltium 365で可能なことの表面をかすめただけです。今日からAltium Designer + Altium 365の無料トライアルを開始してください.