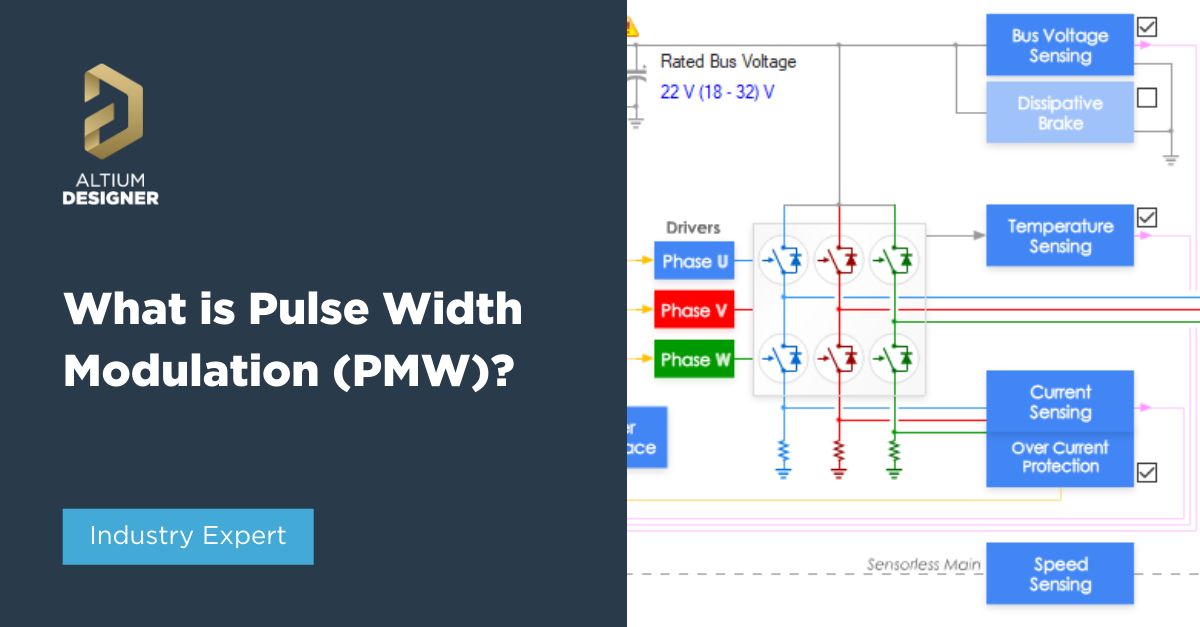

電源設計におけるPWM

スイッチモード電源は、その名の通り、半導体スイッチ(通常はMOSFET)を使用して磁気コンポーネント(通常はトランスまたはインダクタ)を駆動します。スイッチングされた電力回路の出力はその後、整流され、規制されて直流出力を提供します。スイッチモード電源は、リニアレギュレータなどの非スイッチング代替品よりもはるかに高い効率性のために人気があります。この記事では、PWM制御とは何か、そしてそれをどのように使用するかについて取り組みます。

PWMとは

パルス幅変調(PWM)、またはパルス持続時間変調(PDM)としても知られている、は交流(AC)信号の平均電力を減少させる技術です。PWMの意味は、信号の基本周波数に影響を与えることなく平均電圧を減少させるために波形の一部を効果的に切り取ることです。電圧が「オフ」の期間を増やすことで平均電圧が減少し、したがって電力が減少します。

電源または電力レギュレーターでPWMが適用される場合、PWMは以下のいずれかを維持するために適用されます:

- 変動する電圧で一定の電流出力(電流モード制御)

- 変動する電流で一定の電圧(電圧モード制御)

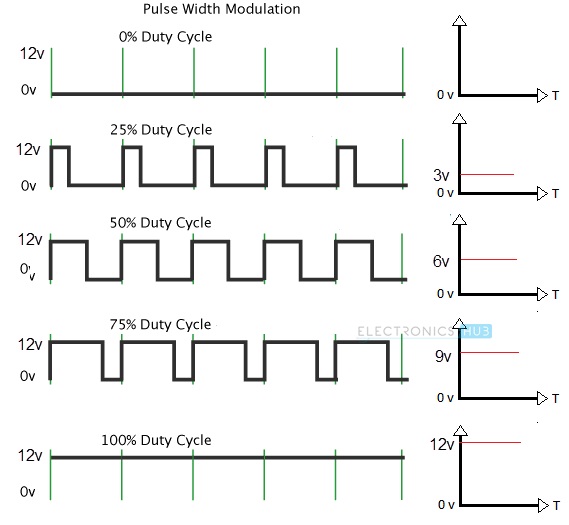

以下でさらに詳しく説明します。PWM信号の時間領域波形を見ると、次の画像のような波形になります。

画像出典:ElectronicsHub

PWM出力制御の使用

スイッチモード電源は、負荷条件の変化に伴って所要の限界内で出力PWM電圧制御を維持するために、フィードバック制御ループを実装する必要があります。電源の出力電圧はエラーアンプを通じてフィードバックされ、制御信号を提供します。PWMの使用が最も一般的な制御方法です。電源の入力におけるAC信号のパルス幅を調整して、電気エネルギーを増減させ、これが電源の出力電圧の変化に変換されます。例えば、入力パルス幅を増やすと出力電圧が上昇し、パルス幅を減らすと出力PWM電圧制御が低下します。このメカニズムは出力電圧の閉ループフィードバック制御を提供します。

考慮すべき一つの問題は、典型的なAC波形は、穏やかな立ち上がりと立ち下がりのエッジを持つ傾向があるということです。PWM電源制御が適用されると、特にデューティサイクルが小さい場合、立ち上がりと立ち下がりのエッジがより急激になることがあります。突然の電圧変化は過渡現象を発生させ、電磁ノイズに寄与し、PWM回路内で大きな突入電流を引き起こす可能性があります。また、制御回路のわずかなエラーが、出力の大きなエラーに拡大され、不安定な出力電圧を引き起こす可能性があります。標準的な解決策は、入力波形の急激なオンオフ切り替えを避け、代わりにスロープ補償技術を使用して変化率を制限することです。

ピーク電流モード制御(PCMC)技術は、インダクタ-インダクタ-キャパシタ(LLC)コンバーターが電圧モード制御を必要とする場合を除き、パルス幅変調(PWM)電源回路に対して簡単な解決策を提供します。デューティサイクルが最大値に近づくと、PWM電源制御は常に課題となります。この状況を避けるためにPWM回路を設計することは、出力の不安定を防ぐためにスロープ補償を適用する追加の制御回路を追加するよりも常に好ましいです。

設計上の考慮事項

過渡的な起動電流

スイッチモード電源を使用する際の欠点の一つは、特に絶縁型電源で使用される場合、スイッチオン時に電源の誘導要素がエネルギーを帯びることによって大きな過渡電流が発生する可能性があることです。さらに、初期電流は予測不可能であり、誘導要素が最初にエネルギーを帯びるACサイクルの正確な点によって変動します。

過渡応答は、SPICEシミュレーションで簡単に予測できます。レギュレータの正確なモデルが常に必要なわけではありません。FETを制御し、デバイス内の実際のPWM信号の立ち上がり/立ち下がり時間を模倣するPWM信号だけが必要です。これは、Hブリッジなどの外部FETを制御するために使用されるゲートドライバーに対して、合理的に正確な結果を提供します。以下の例は、バックコンバーター内のパッシブ部品のESRが不十分で、オン時の最初の500ms間にLC回路の特徴である過減衰応答につながるケースを示しています。

PWMベースの制御回路は、ソフトスタート機能を実装することができ、初期の電源投入フェーズを制御してPWM回路に利用可能なエネルギーを制限し、電源が安定状態に達するまで励磁電流を制限することができます。本質的に、これは上記の振動が発生しないように減衰した電源投入を生み出すでしょう。初期サージ電流を制限することは、コンポーネントを保護し、過渡電流流れに関連する放射を減少させることができます。

多くの電力レギュレータICはこの機能を含んでおり、デバイス上のピンでアクセス可能です。例えば、Analog DevicesのLTM8052では、SSピンにキャパシタを接続することでソフトスタート時間がプログラムされます。

過電流保護

PWM制御の利点は、出力電流が定義された限界を超えるとPWMをオフに切り替えて電源を無効にするために、電流検出ロジックを使用できることです。これは、電流がその境界内に戻ると自動的にリセットされる、簡単に実装できる過電流保護メカニズムを提供します。

パルス周波数変調による低負荷の管理

スイッチモードPWM電源回路図の主な欠点の一つは、非常に低い負荷での固有の非効率性です。無負荷条件下では、電源制御回路による損失が継続的に発生します。これは、電源の効率がバッテリー寿命を決定するスタンバイモードで長時間動作するバッテリー駆動デバイスにとって問題となる場合があります。

この状況への解決策は、PWM電源回路図の代わりにパルス周波数変調(PFM)を使用することです。ここでは、AC波形のデューティサイクルは変わらず、電源出力の制御はAC入力の周波数を変更することによって行われます。

PFMの主な問題は、はるかに広い範囲の周波数でノイズが発生するため、ノイズフィルタリング設計がはるかに困難になることです。

その他の問題としては、PFM制御はPWM制御よりもかなり大きな出力電圧リップルを生成し、過渡応答時間がかなり長くなる可能性があることです。これらの問題は、特に集積回路など、電圧変動に敏感なコンポーネントを駆動する電源を設計する際に、設計者の仕事を難しくします。

電源チップには、出力負荷に基づいて自動的に切り替わる内蔵デュアルモードPWM回路とPFM制御が現在利用可能です。したがって、PFM制御を低負荷条件に限定することは、放射ノイズや電圧リップルなどの不利な影響を最小限に抑えることになります。

低負荷でのパルススキップ変調による管理

低負荷条件を管理する別の技術は、PWM波形を短期間オフに切り替え、この期間中に電源の出力キャパシタが出力電圧を維持することに依存することです。このPWM波形を無効にするプロセスは、パルススキップまたはパルススキップ変調(PSM)として知られています。無負荷条件下では、電源自体の損失を補うために、PWM波形を短期間で断続的に有効にするだけで済みます。

PSM対応電源レギュレータの波形を示す例は以下にあります。PSM機能は、コントローラの内部回路で定義された条件下でFETゲートへのPWMパルスを排除します。以下の例は、テキサス・インスツルメンツのTPS61175からのものです。

結論

PWM回路を使用する主な利点は、非常に高い効率のおかげで非常に低い電力損失があることであり、最適な回路設計のために非常に高い周波数を利用します。また、電源設計のための比較可能な技術と比較して実装コストが比較的安価であり、高負荷を扱う能力があります。主な欠点は、低負荷を管理するために必要な追加の複雑さです。しかし、PWM制御と自動低負荷管理を組み合わせた統合デバイスの利用可能性が、電源設計者のこのタスクを簡素化しました。

次のPCB設計でAltium Designerがどのように役立つかについてもっと知りたいですか?Altiumの専門家に相談してください。