PCB EMI/EMC ガイドライン:あなたの設計でEMI/EMC基準を満たす

もし、携帯電話を2台並べたら、突然どちらも正常に動かなくなったらどうでしょう?幸いにも、このようなことは起こりません。なぜなら、設計者や製造業者が、これらのデバイスが導電性および放射性の電磁干渉(EMI)に関するEMC基準に準拠するように、真剣な努力をしているからです。どのデバイスも、市場に出る前にEMC基準を満たしている必要があります。

これは複雑に聞こえるかもしれませんが、次のデバイスがEMCテストに合格するのを助けるための、いくつかのシンプルな設計戦略があります。さまざまなEMC基準団体とその仕様を知ることから始めるのが良いでしょう。

PCB設計のためのEMC/EMI基準

EMC基準は、規制基準と業界基準の2つの広いカテゴリーに分かれます。あなたの設計のための規制基準は、製品を市場に出して販売したい場所(必ずしもそれが設計されたり製造されたりする場所ではない)に依存します。最初のEMC基準のいくつかは、1979年にアメリカ合衆国連邦通信委員会によって確立されました。その後、ヨーロッパ共同体が独自のEMC基準を定義し、これが将来の欧州連合基準の基礎となり、現在はEMC指令として知られています - 正式には欧州議会の電磁両立性(EMC)指令2014/30/EUと命名されています(こちらからヨーロッパの基準を見ることができます)。

業界標準への適合は、法的な問題だけでなく、特定の環境やアプリケーション領域で展開される電子機器の一貫性と相互運用性を保証するための業界固有の問題でもあります。効果的に、業界のEMC標準は、製造、組立、性能などの他の業界標準と同じ役割を果たします。EMC要件を定義する主要な業界標準機関および規制機関には、

- 米国連邦通信委員会(FCC)

- 米国連邦航空局(FAA)

- アンダーライター・ラボラトリーズ(UL)

- アメリカ無線技術委員会(RTCA)

- 国際電気標準会議(IEC)、通じて国際特別無線障害委員会(CISPR)

- 国際標準化機構(ISO)

- 自動車技術者協会(SAE)

- 電気電子技術者協会(IEEE)

- 米国軍を通じてのMIL-STD標準セット

IECおよびCISPRの標準はヨーロッパでより人気がありますが、IEEEの標準は米国でより人気があります。特に、IEEEの標準はアンテナ校正試験の基礎を形成します。MIL-STDのEMC要件は、世界で最も厳格な標準の中の一つであり、電子機器の商業セクターに適応される最初の標準のいくつかでした。

EMC標準に準拠するための広範な要件

企業が非準拠のデバイスや製品をリリースした場合、警告を受けるか、多額の罰金を科される可能性があります。EMC要件を満たさないことは、安全上の懸念をもたらすだけでなく、企業の評判を損なうことにもなります。EMCに配慮して設計することで、製造ラインから製品が出た後に民事罰を受けることがないようにすることができます。設計者は、EMIを以下の二つの観点から考慮することによって、EMC基準を遵守するための措置を講じます:

-

EMI耐性のための設計:近くのデバイスからの望ましくないEMIに耐えるようにデバイスを設計します。これは通常、適切なスタックアップとルーティング戦略から始まります。

-

放射されるEMIの抑制:デバイスが放出する放射を最小限に抑えるように設計します。ここでは、レイヤースタック、グラウンディング戦略、コンポーネントの配置、そして場合によってはシールドがすべて役割を果たします。

-

伝導されるEMIの抑制:伝導されるEMIには、結合された共通モードや差動モードノイズ、SMPSレギュレータからのスイッチングノイズ、またはグリッドから受け取った高調波など、いくつかの形態があります。

-

高速過渡または電力変動:このタイプのノイズは、注入されたパルスのシリーズ、短期的な電圧低下、周期的な低下、または電力スパイクとして現れます。設計では、これらが出力や負荷にノイズとして現れないようにする必要があります。これらの要件は、それぞれ短いケーブルまたはAC入力を持つ設計に適用されます。

-

サージとESDの抑制:EMI/EMCについて話し合う際、通常はノイズに焦点を当てますが、EMC基準に準拠する設計では、サージとESDに耐えることも重要な側面です。

近接場プローブを使用した放射EMC測定

EMC基準テストに合格する可能性を高めるためのいくつかの戦略

設計者が基本的なEMCチェックに合格するために使用すべきいくつかの基本的な設計実践があります。

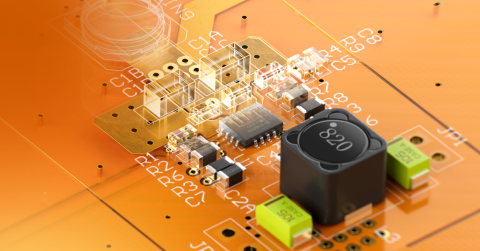

スタックアップ、電源、およびグラウンディング

EMCコンプライアンス戦略は、レイヤースタックから始まります。低インダクタンスのグラウンドシステムを備えたボードを設計することは、EMIの感受性を最小限に抑える最大の効果を持ちます。多層ボードの場合、ループインダクタンスを最小限に抑えるために、信号層の直下にグラウンドプレーンを配置する必要があります。

低レベル信号の干渉は、信号対雑音比を低下させます。したがって、これらの信号を内部層でルーティングすることが良い考えです。スタックに十分な層がある場合、これらのトレースを2つのグラウンドプレーンの間に配置し、その後、最も下のグラウンドプレーンの下に電源プレーンを配置します。電源プレーンをグラウンドプレーンに近づけることで、強力な静電容量結合が提供されます。電源プレーンのノイズや伝導EMIは、信号を干渉させるよりも簡単に近くのグラウンドプレーンに流れ込みます。

内部層から表面層へ信号をルーティングする際は、密接な結合を維持する必要があるため注意してください。基準平面との結合を維持するには、グラウンドプレーンと表面層の間に近くに平行なビアを配置します。クロックのルーティングや配置など、他のEMC問題も問題となり、特に多層PCBで基準平面を変更する場合には、過剰なノイズが発生することがあります。可能であれば、外部参照オシレータを必要とするプロトコルの使用を避け、組み込みクロックを持つプロトコルを使用してください。DDRのようなプロトコルは、ソース同期差動ペアクロックを使用しており、単端クロック接続よりも放射EMIが低くなります(差動ペアに関しては以下を参照してください)。

シールディングの組み込み

放射EMIに対するボードの免疫を提供する別の戦略として、シールディングの慎重な使用があります。これは、ボードから放射されるEMIも抑制します。無線デバイスを扱っている場合は、アンテナをシールディングの外側に配置することで、依然として信号の送受信が可能です。

最もシンプルな解決策は、敏感なコンポーネントやトレースの周りにファラデーケージを形成する接地シールドを使用することです。すべての設計やコンポーネントがこの解決策を受け入れるわけではありません。したがって、より複雑なシールディング方法が必要になるかもしれません。ボードの内部に一様なグラウンドプレーンを使用する場合(とにかくこれを行うべきです)、ボードの端に接地されたビアフェンスと銅注ぎ領域のビアステッチングが同様の保護を提供します。

シールディングは放射されたEMIを抑制するために使用できます

シールディング缶は、おそらく誰もが考える最も一般的なシールディング形態ですが、EMIと戦うために使用できる唯一の可能なシールディングタイプではありません。広帯域EMI抑制を提供できる他のユニークなシールディング材料には、次のものがあります:

- RF放射を吸収する導電性フォームまたはエラストマーガスケット材料

- エンクロージャに取り付けることができるワイヤーメッシュ材料

- 接合面や基板の一部の場所に使用できる金属テープ

- 問題のある周波数帯での吸収を持つコンフォーマルコーティングエンクロージャやケーブルアセン

- リに直接取り付けることができるフェライト

これらの他のタイプのシールドは、PCB上で使用される他のソリューションが失敗した場合に、基板またはエンクロージャ内に実装することができます。個人的には、シールド缶とこれらの他の材料のいくつかは、基板レベルのソリューションの全範囲を実装した後にのみ使用することをお勧めします。

ミックスドシグナルのレイアウトとルーティング

一部のデバイスはデジタルデータを操作し、アナログ信号をサポートする必要があり、それによって本質的に混合信号デバイスとなります。デジタル部分、低周波アナログ部分、RFアナログ部分をPCBレイアウトの異なる領域に分けることを試みるのは良い考えです。これらのセクションがそれぞれ専用のグラウンド層エリアを持つことを確認することは常に良いことですが、グラウンド層は連続しているべきです。これは、基板周りのリターンパスを追跡することがここでの課題であることを意味します。目標は二つあります:異なる基板セクション間の干渉を防ぎつつ、隣接層の上でグラウンドを経由してルーティングすることにより、信号が巨大なループインダクタンスを持たないようにすることです。混合信号のグラウンディング戦略についてもっと学ぶには、この記事を読んでください。

電源バス上のバイパス/デカップリングキャパシタ

最後に、電源バスのノイズがEMIを生じさせ、これが基板の端から放射される可能性があることを理解することが重要です。これには、適切なスタックアップ設計、バイパス/デカップリングコンデンサの配置、および参照/電源プレーンペアの配置が必要です。多くのI/Oを持つ先進的なデジタルシステムにおける電源バスのノイズの低減は、電力整合性の問題であると同時にEMI/EMCの問題でもありますので、これらの問題に対処するために電力整合性の基礎を理解することに焦点を当ててください。

PCB設計のためのEMI/EMC基準に向けて設計するには、ボードレベルのソリューションを実装するための適切なレイアウトツールが必要です。Altium Designer®は、準拠したレイアウトを作成するために必要なすべてを提供するだけでなく、必要に応じて作業を再実行することもできます。Altium Designerは、SI、PI、およびEMI/EMCシミュレーションのための最先端アプリケーションとの統合も提供する業界をリードするCADプラットフォームです。設計が完了し、製造業者にファイルをリリースしたい場合、Altium 365™プラットフォームはプロジェクトの共有やコラボレーションを容易にします。

Altium DesignerとAltium 365で可能なことの表面をかすめただけです。今すぐAltium Designer + Altium 365の無料トライアルを開始してください。