PCB設計におけるEMI制御の習得:低EMIのためのPCB設計方法

Mastering EMI Control in PCB Design Series

How to Design PCBs for Low EMI

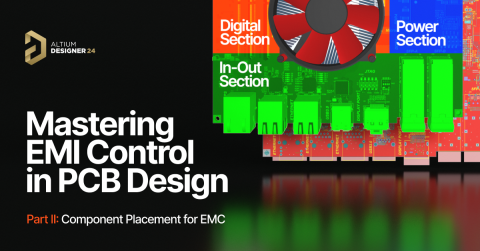

| January 14, 2025PCB設計におけるEMI制御をマスターするシリーズの第4回目へようこそ。PCB設計におけるEMI制御のマスタリング。この回では、効果的なPCB設計に不可欠な電磁干渉(EMI)の管理に関する高度な側面を探ります。

プリント基板(PCB)を設計する際の主な課題は、設計が放射された排出と導かれた排出の両方のテストに合格できるようにすることです。これは、規制基準を満たし、意図した環境でPCBが適切に機能し、他のデバイスやシステムへの干渉を引き起こさないようにするために重要です。

同様に重要なのは、外部および内部の排出に対する免疫を達成することで、最終製品の信頼性と性能を確保することです。

図1 - Altium Designer®でのPCB設計の例

電磁干渉(EMI)の設計では、排出は主に回路内の電流の変化によって引き起こされることを理解することが重要です。これは、内部の電流変化により、すべての回路が必然的にある程度の電磁放射を発することを意味します。設計者にとっての主な課題は、この放射の程度を管理し制御することです。

より良い電磁両立性(EMC)を達成するためには、これらの電磁放射を効果的に含有し最小限に抑えるプリント基板を設計することに焦点を当てる必要があります。

これには、2つの主要なタイプの放射を対処することが含まれます:

- 差動モード電流による放射;

- 共通モード電流による放射。

図2 - 回路内の差動モード電流と共通モード電流(共通モード電流の戻り経路は示されていません)。参照:Dario Fresu

これらの電流を理解する最も簡単な方法は、差動モード電流を異なる経路を通って「反対方向」に流れるものと考えることであり、共通モード電流は回路の経路に沿って同じ「共通」の方向に流れます。

差動モード電流からの放射を最小限に抑える方法

差動モード電流は、回路の正常な動作に不可欠です。これらの電流は、集積回路(IC)とコンポーネントの間を流れ、PCB内の回路の設計の一部です。

これらは、回路レイアウトによって定義されたループ内を移動し、これらのループのサイズは、生成される放射レベルに影響します。ループが大きいほど(つまり、面積が大きいほど)、放射は高くなります。さらに、高い周波数は放射を増加させます。

これらの放射を減らすために、いくつかの戦略があります:

- トレースを通る電流の量を減らす

- 電流の周波数を下げる

- 電流ループの面積を最小限にする

電流と周波数を減らす(オプション1と2)は、回路の効率に大きな影響を与える可能性があるため、しばしば非現実的です。最も実用的なアプローチは、これらの電流ループによって囲まれる面積を最小限にすることで、PCB設計者がより直接的に制御できます。

図3 - Altium Designer®を使用したPCB内の電流ループの例

非常に効果的な方法は、レイヤースタックアップ内で信号トレースに近いリターン参照面を使用することです。これにより、前方およびリターン電流によって囲まれる面積が非常に小さくなり、放射を最小限に抑えます。これに加えて、信号トレースを可能な限り短く保つことで、差動モード電流からの放射を減らす上で最良の結果が得られます。

もちろん、コンポーネントの配置、信号のクロストーク削減、近くのケーブルにノイズを伝達する可能性のある他の結合メカニズムの管理も、放射を減らすために重要です。しかし、これらの要因は、電流ループの面積を最小限にするという主要な技術に次ぐものです。

この技術は、差動モード電流の放射の根本原因に対処するため、放射を減らす上でより直接的で、かつ大きな影響を与えます。

共通モード電流からの放射を最小限に抑える方法

設計者が認識する必要があるもう一つの重要な電流のタイプは、共通モード電流です。差動モード電流が回路に意図的に設計されているのに対し、共通モード電流は回路図に明示的に計上されていません。これらの電流は回路の動作に必要なものではなく、主に設計内の寄生要素から生じます。

これらの寄生電流を特定し、制御することは、その源が常に明らかでないため、かなり難しい場合があります。共通モード電流は、通常、差動モード電流が回路内の寄生要素を通過するときに生成されます。

図4 - リターンプレーンのギャップは、共通モード放射の原因となることがよくあります (Altium Designer®)

これらの寄生要素は、一般に「グラウンド」または「シグナルグラウンド」として知られるリターン参照導体に特に見られます。リターン参照導体の寄生要素に関する問題は、主に、実際には、コンポーネントや導体が完璧ではなく、理想からは程遠いために生じます。

例えば、回路内の銅トレースは抵抗だけでなく、インダクタンスやキャパシタンスも示します。これらの寄生特性は、信号周波数が上昇するにつれて、ますます重要になります。

差動モード放射とは異なり、主に電流ループのサイズに影響されるのに対して、コモンモード電流は主に導体の長さとノイズの周波数によって影響を受けます。しかし、導体の長さの影響はある点を超えるとそれほど重要ではなくなりますが、この記事ではそれ以上には掘り下げません。

電気的に短いケーブルの場合、コモンモード電流放射はループアンテナ伝送ではなく、ダイポール(またはモノポール)アンテナ伝送としてモデル化できます。このモデリングの変更は、放射がどのように生成され、制御されるかに影響を与えます。

コモンモード電流からの放射をソースで効果的に減らすためには、次の戦略を考慮する必要があります:

- コモンモード電流の量を減らす;

- コモンモード電流の周波数を下げる;

- コモンモード放射に寄与する導体の長さを最小限に抑える。

重要な戦略の一つは、信号トレースの長さを短縮することに焦点を当てることです。システムの制約のためにすべての導体を短くすることが常に可能ではないかもしれませんが、設計者は可能な限りトレースの長さを最小限に抑えるよう努めるべきです。この努力は、特に信号周波数が上昇し続けるにつれて、PCBからの放射を軽減するのに役立ちます。

固体の銅面を返りおよび参照面として使用することも、もう一つの効果的な技術です。この方法は、返り電流が通過しなければならないインダクタンスを減少させ、これらの放射を駆動する共通モード電圧源を減少させます。

返り電流のための低インピーダンス経路を提供することにより、分割や切断がない固体の銅面は、信号の整合性を維持し、EMIを減少させるのに役立ちます。

放射を最小限に抑える方法 ステッチングビアの使用

複数の返り参照面を持つ多層スタックアップでの共通モード放射を減少させるために推奨される別の技術は、これらの面の間にステッチングビアを使用することです。ステッチングビアは、異なる返り参照層を接続し、それらが同じ電気的ポテンシャルに留まるようにします。この接続は、双極子(または単極子)アンテナモード放射を駆動する共通モード電圧源を減少させるのに役立ち、望ましくないノイズやEMIを大幅に減少させることができます。

図5 - Altium Designer®でのステッチングビアの例

共通モード放射を減少させるだけでなく、ステッチングビアは、スタックアップ内の層間で信号が移行する際の信頼性のある電流返り経路および参照ポテンシャルを提供するために不可欠です。これにより、面と面の間で発生する可能性のある放射が防止され、EMIだけでなく、信号の整合性やPCBの全体的な性能にも干渉することがあります。

結論

電磁干渉(EMI)制御を効果的に念頭に置いてプリント基板(PCB)を設計する際には、適切なツールを持つことが不可欠です。高度なPCB設計ソフトウェアを使用すると、さまざまな設計パラメータを管理し、ボードが卓越した精度と効率で作成されることを保証できます。これらのツールは、複雑な設計要件を処理し、EMI軽減戦略が正しく適用されていることを確認するために重要であり、より信頼性が高く、高性能なPCBにつながります。

Altium Designer®は、この分野で優れたツールとして際立っており、設計ワークフローにシームレスに統合されます。PCB設計に対するあなたの専門知識と情熱を十分に活用するために必要な柔軟性と高度な機能を提供し、効果的なEMI制御戦略を実装することを容易にします。

PCB設計を洗練させ続けるためには、情報を得続けることが重要です。次の記事では、電力分配ネットワーク(PDN)のデカップリング戦略について取り上げ、設計実践を改善するためのさらなる洞察を提供します。

最新のアップデートや貴重なコンテンツを見逃さないように、Altium®のページやソーシャルメディアチャンネルをフォローしてください。

高度なPCB設計ツールの利点を直接体験してみましょう。今すぐAltium Designer® + Altium 365™の無料トライアルを始めてください。一流のデザイナーのコミュニティに参加し、これらのツールがどのようにあなたの作業を大幅に向上させることができるかを確認してください。