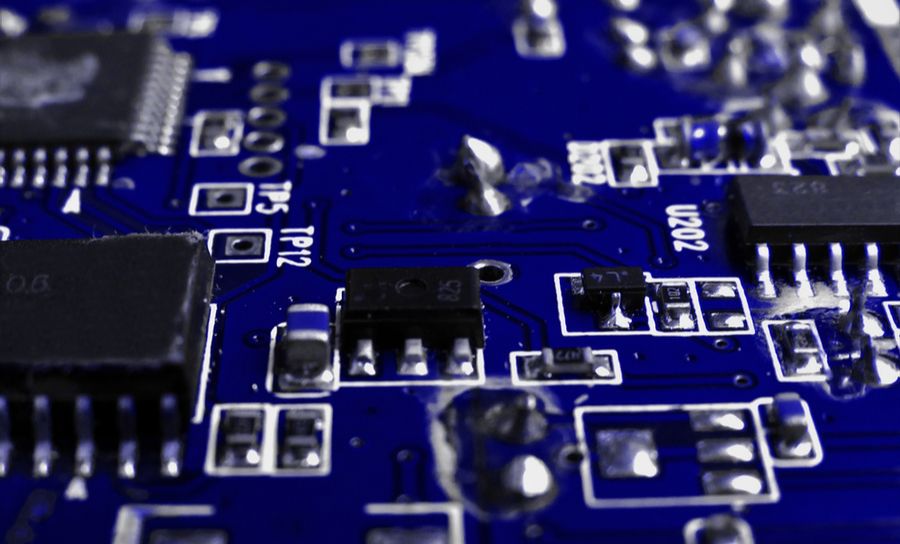

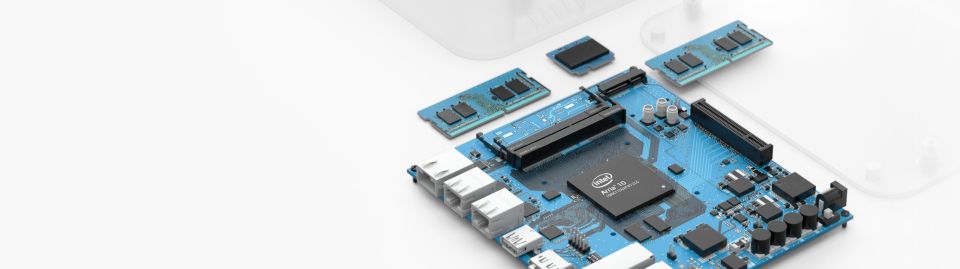

高速PCB設計

高速PCB設計では、高速エッジの信号が使用されます。この信号では、デバイスの状態が非常に速く切り替わり、信号がコンポーネント間を移動し終わる前に移行が完了します。高速PCB設計における相互接続には、正確なインピーダンス整合が必要であり、相互接続に伴って起こりうる損失、歪み、EMI、クロストークを考慮した配線が必要です。伝送線路の設計、レイアウト、ルーティングを適切に行うことで、これらの問題を最小限に抑えることができます。プリント基板における高速基板レイアウトや伝送線路設計を成功させるためのリソースを、ライブラリでご覧ください。

Filter

見つかりました

Sort by