HDIとは?設計の基本とHDI基板製造プロセス

テクノロジーが進化するにつれ、より多くの機能をより小さなパッケージに詰め込むことが必要になってきました。HDI(高密度接続)技術を用いて設計されたPCBは、より小さなスペースに多くの部品が詰め込まれるため小型化する傾向にあります。HDI PCBでは、ブラインドビア、ベリードビア、マイクロビア、パッド内ビア、極細トレースなどが使用され、より多くの部品が小さな面積に詰め込まれています。HDIの設計の基本と、Altium Designer®が強力な HDI基板設計の作成にどのように役立つかを説明します。

HDI(高密度接続)基板の設計・製造は、1980年にPCBのビアサイズを小さくする方法が研究され始めたことに始まります。量産型のビルドアップやシーケンシャルPCBが初めて登場したのは1984年でした。以来、設計者や部品メーカーは、より多くの機能を1枚のチップや基板に詰め込めるよう常に奮闘してきました。現在、HDI基板設計と製造は、IPC-2315、IPC-2226、IPC-4104、IPC-6016の各規格で定められています。

HDI基板の設計を計画する際には、設計上および製造上の課題があります。ここでは、HDI基板を設計する際によく出てくる課題をいくつか簡単にご紹介します。

- 基板における限られたワークスペース

- 小型部品と極狭のスペーシング

- PCBスタックアップの両側における部品数の多さ

- 信号の通信時間を長くする、長いトレースルート

- 基板作成に必要なトレースルートの多さ

ルール駆動型設計エンジン上に構築された適切なレイアウトおよびルーティングツールのセットを使用すると、PCB設計の通常のルールに捉われず、非常に高い相互接続密度を備えた強力なPCBを作成できます。HDI PCBボード設計用に構築された高度なPCB設計ソフトウェアを使用すると、高密度PCBルーティングおよびファインピッチコンポーネントの操作が簡単になります。世界トップクラスのAltium Designerの設計機能を使って、新しいHDIを設計し、HDIの製造プロセスを計画することができます。

HDI基板設計と製造の違い

HDI製造プロセスは、従来のPCB製造プロセスとはいくつかのシンプルかつ重要な点で異なります。ここで重要なのは、製造業者の限界により設計自由度が制限され、基板の配線方法にも限界がもたらされるということです。極細トレース、極小ビア、多くのレイヤー、極小部品の使用は、設計ソフトウェアで対応することができますが、製造容易性設計(DFM)要件に対応するには、設計ソフトウェアの自動化機能を活用する必要があります。正確なDFM要件は、基板を作るのに使用される製造プロセスや材料によって異なります。DFM要件は信頼性要件でも重要になります。

次のことを念頭において材料を選択してください。

- 絶縁体には、コア基板材料で使用されている現在の化学物質に適合した化学物質が使用されているか?

- 絶縁体のメッキ銅の接着性に問題はないか?(多くのOEMでは、6 lb./in超、1オンスあたり1.08kgm/cm、35.6µmの銅の使用が求められています)

- 絶縁体は、金属層の間に適切かつ信頼できる絶縁体間隔があるか?

- 熱要件を満たすか?

- 絶縁体は、ワイヤーボンディングやリワークに適した「高い」Tgを提供するか?

- 複数のSBU層での熱衝撃(例:ハンダフロート、加速した熱サイクル、複数回のリフロー)に耐えられるか?

- メッキ加工された信頼性の高いマイクロビアが使用されるか?

HDI PCBに使用される一般的な絶縁体の材料には9種類あります。IPC-4101BやIPC-4104AなどのIPCスラッシュシートは、これらの多くに対応しますが、IPC規格ではまだ規定されていないものも多くあります。材料としては次のものが使用されています:

- 感光性液体絶縁体

- 感光性ドライフィルム絶縁体

- ポリイミドフレキシブルフィルム

- 熱硬化型ドライフィルム

- 熱硬化性液体絶縁体

- RCC(レジンコート銅)箔、(2層構造・強化構造)

- 従来のFR-4コア・プリプレグ

- 新しい「スプレッドグラス」レーザードリルブル(LD)プリプレグ

- 熱可塑性樹脂

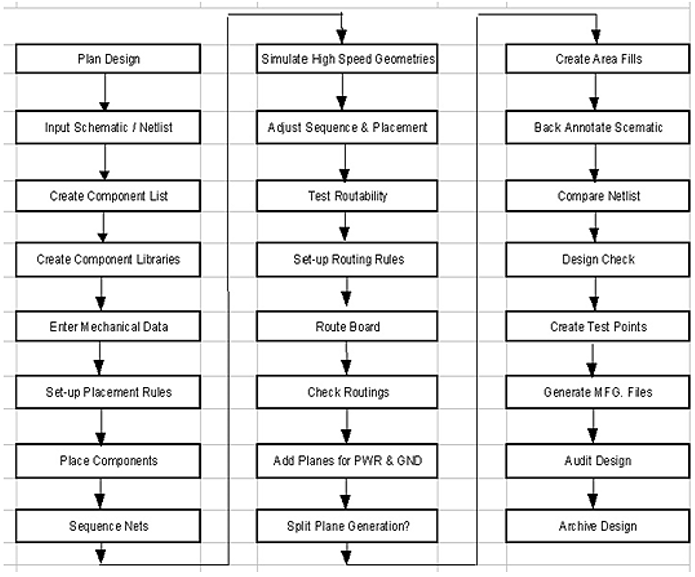

以下はHDI基板の設計プロセスです。HDIの配線効率は、スタックアップ、ビアアーキテクチャー、部品の配置、BGAのファンアウト、設計ルールなどに左右されます。HDIレイアウトを計画する上で最も重要なことは、トレース幅、ビアサイズ、BGA部品の配置/エスケープ配線を考慮することです。

HDI基板設計とレイアウトプロセスの一般的な概要。

HDI基板の製造方法については、必ずメーカーに確認してください。レイアウトに配置できる形状に影響するため、製造方法の限界を見極める必要があります。BGA部品のボールピッチにより使用するビアサイズが決まり、それによって基板を作るために必要なHDI製造プロセスが決まります。HDI基板の機能の1つであるマイクロビアは、層間の配線を考慮して正確に設計する必要があります。

HDI基板設計と製造プロセスの概要

一般的な基板の製造プロセスにはいくつかの工程がありますが、HDI基板の製造では、他の基板では使用されていない可能性のある特殊な工程があります。HDIの設計プロセスは、他の多くのプロセスと同じように、次のように始まります。

- 基板上の最大のBGA部品を使用するか、基板上の最大ICのインターフェース+方向数を使用することにより、すべての信号を伝送するために必要な層数を決定します。

- PCBスタックアップを作成するために、材料を選択し、絶縁体データを得るために、メーカーに連絡します。

- 層数と厚さに基づいて、内層を経由して信号を伝送するためのビアスタイルを決定します。

- 必要に応じて信頼性評価を行い、アセンブリ中や動作中に材料が相互接続にストレスを与え、接続を阻害しないことを確認します。

- 製造業者の能力と信頼性要件(ティアドロップ、トレース幅、クリアランスなどに対する要件)に基づいて設計ルールを決定し、信頼性の高い製造とアセンブリを実現します。

スタックアップの作成と設計ルールの決定は、基板の配線能力と最終製品の信頼性を決定する重要なポイントです。これらが完了すると、設計者は製造業者のDFM要件と信頼性要件をECADソフトウェアの設計ルールとして実行することができます。これをフロントエンドで行うことは非常に重要で、設計の信頼性、ルーティング、製造性の確保に役立ちます。

HDIのDFM要件を満たす形状の設計

HDI基板のクリアランスに関するDFM要件は非常に厳しいものですが、PCB設計ソフトウェアの設計ルールを活用することで対応可能です。レイアウトや配線の前には次のDFM要件を把握しておくことが重要です:

- トレース幅とスペーシング制限

- アニュラリングとアスペクト比の制限(特に高信頼性設計の場合)

- 必要なスタックアップでインピーダンスを制御するために基板に使用される材料システム

- 希望のスタックアップまたはレイヤーペアのインピーダンスプロファイル(利用可能な場合)

これらのDFM要件を満たすようにHDI基板を設計するには、設計ツールが極めて重要です。適切な設計ツールを使えば、HDI基板にインピーダンス制御されたトレースを配線することは非常に簡単です。インピーダンスプロフィールを作成し、メーカーのDFMガイドラインを考慮しながら、必要なトレース幅を定義するだけです。HDIレイアウトを作成する際には、配線ソフトウェアのオンラインDRCエンジンが配線をチェックします。HDI DFMの関連ルールをすべて考慮していることを確認するために、製造業者が製造プロセスで使用する仕様書をすべて入手してください。

HDI PCB配線におけるビアの種類

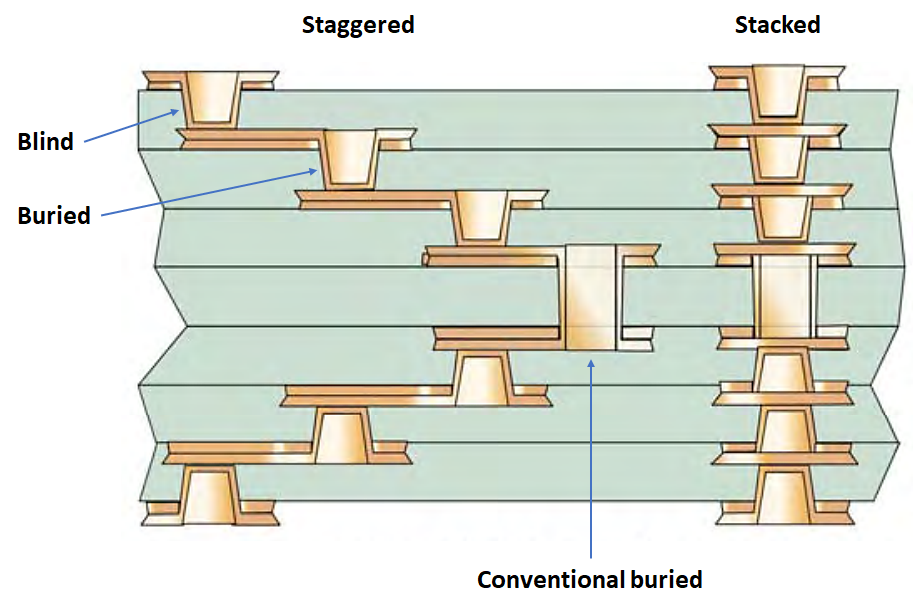

下図は、HDI基板のレイアウトや配線で使用される典型的なビアのスタイルを示したものです。これらのビアスタイルは、アスペクト比が(理想的には)1未満と低くに設定されていますが、メーカーによってはスタックドマイクロビアを含めてアスペクト比2までの信頼性を謳っている場合もあります。PCBスタックアップの中央には、従来のベリードビアがあり、厚いコア層を介した接続を実現しています。この内層にあるベリードビアは、機械で多少の穴を開けるのでアスペクト比を大きくすることができます。層数と絶縁体の厚さが決まれば、設計者は上記のアスペクト比の制限に合わせてビアを設計することができます。マイクロビアのアスペクト比の制限を守ることは、特にリフローを経た基板や、熱的・機械的なショックやサイクルが繰り返される環境に置かれた基板の信頼性を確保するために重要です。

シーケンシャルビルドアップ

HDIスタックアップ構造を層ごとに構築するために、主にシーケンシャルラミネーションプロセスが使用されます。一般的に、この技術はどんな多層プリント基板でも使用できますが、HDIの場合は特に重要です。これは、高密度で非常に薄い絶縁体が、厚いコアの周りに個々の層で形成されるため、複数のラミネーションによりスタックアップを構築するからです。シーケンシャルラミネーションプロセスは、次の工程で構成されています:

- フォトレジストの蒸着と露光:これは、エッチングする領域を定義するために使用され、ラミネート上に導体のパターンを残します。

- エッチングと洗浄:現在の業界標準のエッチング液は、塩化第二鉄エッチング液です。エッチング後、残ったフォトレジストを再生し、得られた導体パターンを洗浄します。

- ビアの形成と掘削:ビアは機械的またはレーザーによる掘削で外形を定義します。ビア密度が高い場合は、ビアホールを化学的に除去することができます。

- ビアの金属化:ビアの外形が定義されると、連続した導電性相互接続を実現するために金属化されます。

- ビルドアップ:複数のラミネーションサイクルで層を積み重ね、外層処理前にスタックアップを構築します。

以下の「金属化」セクションで、ビルドアッププロセスを示すフローチャートをご覧ください。

HDIでのビア形成

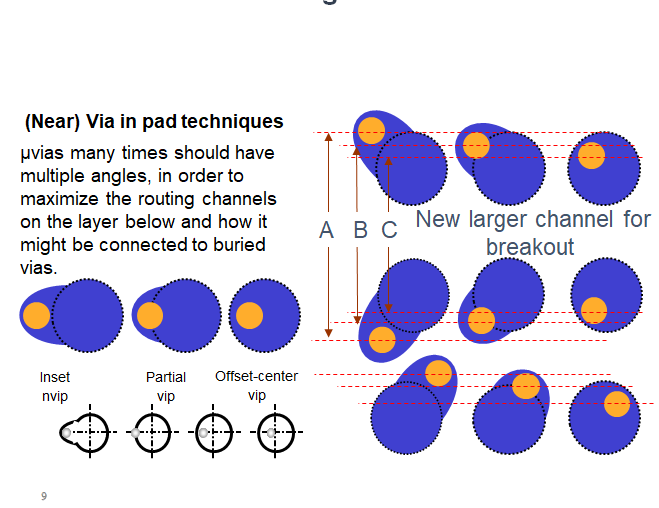

HDI基板では、機械的な穿孔加工でPCBに配置できるビアサイズの下限に近い相互接続が必要になります。ビアの穴が6milよりも小さくなると、層間にマイクロビアを配置するため、別のビア形成プロセスが必要になります。HDI基板では、フィルドメッキされたマイクロビアが標準機能となっているため、ビアインパッドの設計手法で使用することで、高密度化を図ることができます。ビアインパッド手法を使用すると、コンポーネントのリード線から内部層への直接接続が可能になるため、より多くのコンポーネントを設計に詰め込むことができます。

マイクロビアの信頼性に不安がある場合は、パッドから外れた極小のトレース部分をマイクロビアに接触させるニアパッド手法を用いることもできます。これにより、内部層への接続が実現し、ドリルの迷走により希望のドリル位置から多少のずれが生じても、より大きなブレークアウトチャンネルが得られます。

HDI基板のビアインパッド手法の設計スタイル。

金属化

HDI基板の各層は、シーケンシャルラミネーションの際に、ビアの金属化、フィル、メッキ処理工程を経ます。そのため、リフローサイクル中や動作中にひび割れが発生しないように、ネック部に十分なラップメッキを施し、内部にボイドフリーのビアを形成する必要があります。HDIの製造では、次のような4つの金属化工程が行われます:

- 従来の無電解メッキおよび電気メッキ加工処理

- 従来の導電性グラファイトやその他のポリマー処理

- 完全無添加、セミアディティブ無電解メッキ処理

- 導電性ペーストまたはインク処理

より大きなビアを穿孔することも可能ですが、穿孔速度が遅くなるためスループットが低下し、最終的にはコストがレーザー穿孔コストを上回ります。レーザードリルはマイクロビアホールの形成プロセスとしては圧倒的に人気がありますが、ビアの形成プロセスとしては最速の方法ではありません。小径ビアのケミカルエッチングは最も高速で、1秒間に8,000〜12,000個のビアを形成することができると予測されます。これは、プラズマビアの形成やフォトビアの形成にも言えることです。

レーザードリルでは、高フルエンスのビームを使って基板のラミネートに穴を開けます。レーザーは、絶縁体材料を除去し、銅回路を遮断する際に停止することができるため、深さを制御したブラインドビアの形成に最適です。レーザーエネルギーの波長は、赤外線と紫外線のリジョンにあります。約20μmという極小ビームスポットサイズ

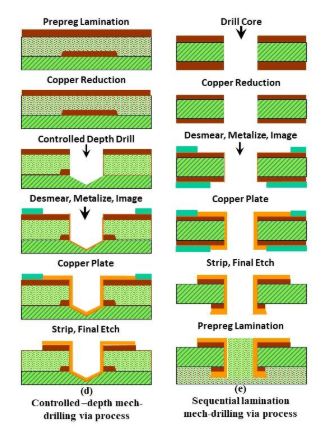

基板のビアがドリルで開けられるほど幅がある場合は、制御ドリル工程でビアを配置することができます。そのためには、2層の基板を接着するための中間シーケンシャルラミネーションの後、ビアバレルの外形を定義するための穿孔・メッキ加工、内層との接続、パッドの上層への配置が必要です。これらのビアは、内層にある場合は次のシーケンシャルラミネーション工程の前に充填され、外層にある場合は充填しないままにしておくこともできます。穿孔およびシーケンシャルの全体的な流れは次の通りです。

HDIの製造プロセスにおけるマイクロビアの穿孔と金属化プロセス。

HDIの製造プロセスに基板を組み込む

HDI基板の製造工程は、従来のリジッド基板の製造工程よりも高度ですが、一般的なリジッド基板に使用するものと同じ製造データセットを使用しています。HDI基板のレイアウトが完成し、DFM審査に合格したら、いよいよ製造業者やアセンブリ業者に成果物を渡す準備をします。Altium Designerの統一された設計環境では、すべての設計データを使用して、新しいHDI基板のGerbers/ODB++/IPC-2581ファブリケーションファイル、ドリルテーブル、部品表、アセンブリ図面を作成します。

HDI基板の設計、レイアウト、製造に最適なソフトウェアパッケージをお探しの場合は、包括的なAltium Designer®の設計ツールパッケージのご利用がおすすめです。統合された設計ルールエンジンとレイヤー構成マネージャー により、HDI基板の製造、インピーダンス値の計算、基板材料システムでの銅の粗さの考慮などに必要なすべての機能が利用できます。デザインが完了し、ファイルをメーカーに送るする場合、 Altium 365®プラットフォームを使用すると、プロジェクトのコラボレーションおよび共有が簡単になります。

ここでは、Altium 365 と Altium Designer で何が可能か、その一部を紹介したに過ぎません。ぜひ、Altium DesignerとAltium 365をご検討ください。Altium Designerの無償評価版をを今すぐ開始しましょう。