DDR3 ルーティングガイドラインとルーティングトポロジ

揮発性メモリがなければ、コンピュータはハードドライブやフラッシュのような非揮発性メモリへの常時読み書きが必要になります。非揮発性メモリは、現代のコンピュータを非常に強力にし、高度なタスクに必要な適応性を与える要素の一つです。DDR3は現在時代遅れになりましたが、DDRベースのメモリはこれからも現代のコンピュータアーキテクチャにおいて中心的な役割を果たし続けるでしょう。適切な設計ツールを使用すれば、最新世代のDDRベースのメモリやそれ以降の設計が可能です。

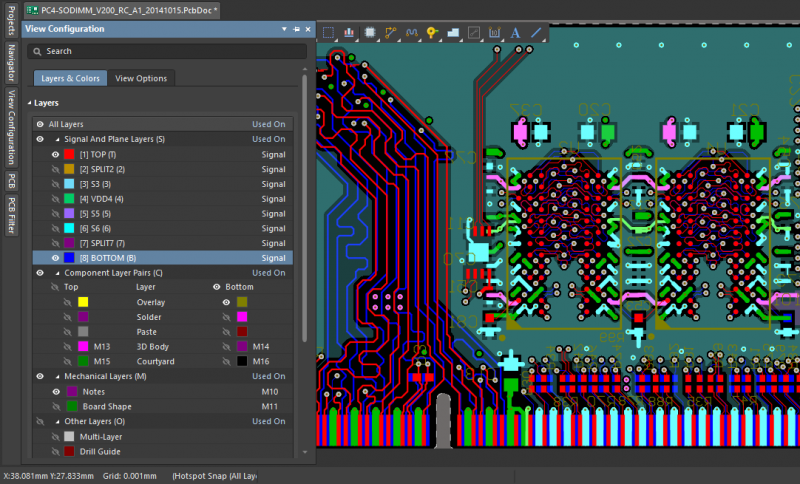

Altium Designerで何ができるか見てみましょう。

高性能PCBとメモリアーキテクチャにおける業界標準のエレクトロニクス設計。

ダブルデータレートスリー(DDR3)は、DDRの以前の世代を継承する動的ランダムアクセスメモリ(DRAM)の一種です。これらのメモリは1066 MHzに達するクロックスピードを持ち、最大24 GBのメモリをサポートします。この高いクロックスピードと大容量のストレージは、DDR3が現代のコンピューティングにおいて主流であり続けることを保証しましたが、最終的にはDDR4に改善されました。新しい世代はデータレートとクロックスピードの限界を常に押し上げており、DDRベースのメモリが近い将来新しいアーキテクチャに置き換えられることはほとんどないでしょう。

このことを念頭に置いて、メモリ設計者はDDRベースのメモリに対する様々なPCB設計ルールを認識し、これらのルールがDDR4でどのように限界まで押し上げられているかを理解する必要があります。設計者は、新しいトポロジの実装がDDRベースのメモリの機能性を向上させたことを含め、PCBの異なるルーティングトポロジにも注意を払うべきです。

Altium Designerのような優れたPCB設計パッケージを使用することで、設計エンジニアはDDR3、DDR4、および将来のメモリ世代のパフォーマンスを向上させるための最適なルーティングトポロジを実装できます。Altium Designerには、設計、インタラクティブルーティング、電力供給分析、およびシミュレーションツールが含まれており、DDRベースの設計が最高のパフォーマンスで動作することを保証するために必要なものがすべて揃っています。

DDR3ルーティングのためのルーティング設計ガイドラインとトポロジ

DDR3は、差動クロック、アドレス、コマンド、および制御信号にフライバイトポロジを使用します。DDR3は元々、メモリバンクをコントローラーに接続するためにTトポロジを使用していましたが、高性能なDDR3メモリは、高容量負荷およびICアーキテクチャとの互換性を向上させるためにフライバイトポロジを使用します。

DDR3またはDDR4の適切なアーキテクチャを実装し、DDR SDRAMダイパッケージとのインターコネクトを配置するには、トポロジを制約しない適応可能なルーティングツールが必要です。信号トレースは差動ペアとしてルーティングされ、PCIeのような他のコンピュータ周辺標準と比較して厳密な許容誤差内で正確に一致させる必要があります。

DDR3およびDDR4ルーティングにおけるシグナルインテグリティ

他のデバイスでシグナルインテグリティを確保するための標準的な設計ルールの多くは、DDR3以降にも適用されます。高性能メモリはフライバイトポロジーを使用しており、これには特定の要件があります。トレースは厳密な許容誤差内で長さを一致させる必要があり、差動ペアは同一層上で密接に結合されるべきであり、各メモリデバイスへのスタブ長は、伝送線効果やスタブ内の共振を防ぐために可能な限り短くする必要があります。与えられたレーングループ内のすべての信号は、伝播遅延の差とスキューを防ぐために同じ層上でルーティングされるべきです。

ボード全体でのルーティングとレイアウトの有効性を検証するためには、設計データを直接組み込んだシミュレーションツールが必要です。反射波形とクロストークを計算するシグナルインテグリティツール内で作業することで、DDR3およびそれ以降のメモリに関する重要な性能基準を満たす設計を確実に行うことができます。

- すべてのトポロジーが直感的なわけではありませんが、PCB設計ソフトウェアのルーティングツールは、必要なDDR3ルーティングトポロジーを簡単に実装できるようにするべきです。

- 適切な設計ソフトウェアを使用すれば、DDR3メモリとCPUのルーティングは難しくありません。Altium DesignerでDDR3メモリとCPUファンアウトをルーティングする方法を学びましょう。

- DDR3は時代遅れになりましたが、DDR4は健在であり、多くの同じアイデアがDDR4メモリにも適用されます。メモリデバイスのDDR4ルーティングについてもっと学びましょう。

メモリデバイスのためのデザインレイアウト構成

DDR3からDDR4、そしてその先へ:何を期待するか

DDR3メモリが時代遅れになり、DDR4に置き換えられ、最終的にはDDR5になると、デザイナーはルーティング要件とトポロジーがより複雑になることを期待するしかありません。シグナル速度は増加し、チップ上のメモリデバイスのルーティングトポロジーは新しいレイアウト制約を課すでしょう。これを念頭に置いて、重要な設計制約を満たしながら、任意のルーティングトポロジーに適応できる設計ソフトウェアが必要です。

設計の一部としてのシグナルインテグリティ

新しい高速または高周波レイアウトでは、優れたシミュレーションツールがボード全体で潜在的なシグナルインテグリティ問題を診断するのに役立ちます。潜在的な問題はレイアウトのどのポイントでも発生する可能性があり、適切なシグナルインテグリティツールを使用すると、クロストークを診断し、終端が必要な場所を特定し、寄生要素がボードにどのように影響しているかを判断することが容易になります。その後、潜在的な再設計をテストし、各イテレーション中に結果を直接比較することができます。

- DDR3およびDDR4のレイアウトには、メモリデバイスが適切な電力レベルを受け取り、基板の周りにホットスポットが形成されるのを防ぐために、電力供給分析が必要です。

- シミュレーションツールを設計ソフトウェアに組み込むと、提案された設計変更を迅速に検証し、基板の機能を損なう前に信号整合性の問題を特定できます。

- DDRが非常に人気のあるメモリアーキテクチャであるため、設計アドバイスを提供できる専門家がたくさんいます。信号整合性を確保するためのこれらのDDRルーティングのヒントをチェックしてください。

Altium Designerにおける設計の一部としての信号整合性

Altium Designer:設計と検証機能の統合

DDRメモリに対する複雑な要求を考えると、設計者はルーティングとレイアウトの段階を容易にしながらも、設計がDDR3、DDR4、およびそれ以降の基本的なレイアウト基準を満たしていることを確保するプログラムが必要です。設計ソフトウェアがルール駆動の設計エンジンの上に構築されている場合、設計機能は基板を構築する際に設計基準に対してレイアウトをチェックします。シミュレーションツールは設計データから直接モデルを構築し、データを複数のプログラム間で移動する必要はありません。

Altium DesignerにおけるDDRメモリ設計

Altium Designerを使用すると、設計基準を満たすかそれを上回るDDR3、DDR4、および新しいメモリアーキテクチャを設計するために必要なルーティング、シミュレーション、および検証ツールにアクセスできます。Altium Designerだけがこれらの機能を単一のプログラムに配置し、他の設計プラットフォームではこれらの機能を異なる環境に分けています。DDR設計に必要なすべてがAltium Designerにあります。

- Altium Designerは、DDR設計に必要な重要なレイアウト、ルーティング、シミュレーション、および検証機能を単一の環境に配置します。Altium Designerの統合設計環境についてもっと学びましょう。

- DDR3およびDDR4はすでに高速メモリアーキテクチャであり、後の世代では信号速度とデータ転送速度がさらに増加することが予想されます。Altium Designerにおける高速設計についてもっと学びましょう。

- DDRベースのアーキテクチャとルーティングの複雑さを考えると、設計者はレイアウトをコントロールしながらルーティングプロセスを自動化するのに役立つルーティングツールを必要とします。Altium Designerにおける自動対話型ルーティングについてもっと学びましょう。

他のPCB設計ソフトウェアプラットフォームでは、これらの重要な設計機能を異なるプログラムに分割しています。Altium Designerを使用すると、単一のプラットフォームで最高のルーティングとトポロジーレイアウト機能にアクセスできます。Altiumは、あなたの成功を確実にするためのリソースも提供します。業界の専門家とのポッドキャストやウェビナー、AltiumLiveフォーラム、広範な知識ベース、設計チュートリアルに即時アクセスできます。

古い設計ソフトウェアの新バージョンに困る代わりに、Altium Designerの統合設計環境で作業してみてください。DDRルーティングとレイアウトに必要なツールに、単一の環境内でアクセスできます。Altium Designerを使用すると、DDR設計の最前線に留まることができます。