Altium Designerで作成されたボードのインピーダンス制御ルーティング

Altium Designerの3Dフィールドソルバーは、インピーダンス制御ルーティングを簡単に行えるようにし、システムのための設計ルールを作成することができます。

コンピューティングの要件とアプリケーションは、これまで以上に高速でデータを処理する必要があります。通信帯域が満たされ始め、新しいコンポーネントが市場に出るにつれて、PCBはより高いデータレートと周波数で動作する必要があります。100G以上の高速イーサネットや、5Gや6Gのような先進的な無線プロトコルなど、ネットワーキングおよびデータセンターアプリケーションは、ミリ波帯を超えても引き続き動作します。

これらの事実は、クロストーク、EMI、リンギング、インピーダンス制御などの信号整合性の問題が、高度なPCB設計においてますます重要になっていることを意味します。解析ツールは、設計段階でPCBの信号整合性の問題を特定し、それに対する洞察を提供する能力が必要です。製造業者から完成した基板を受け取り、テストしたところビットエラーレートが非常に高いことが判明することは誰も望んでいません。これが、製品が市場に出る前に信号整合性の問題の原因を見つけることができるシミュレーションツールが重要になるところです。

Altium Designer®の設計環境には、正確なインピーダンス制御、寄生抽出、および伝搬遅延計算のためにレイヤースタックマネージャーと統合する高度な3Dフィールドソルバーが含まれるようになりました。高度な最適化方法でインピーダンスの公式を使用することに慣れていない場合、この統合設計ツールを使用してインピーダンス制御に必要なトレースのジオメトリを決定できます。ここでは、Altium Designerのルール駆動型設計ワークフローでこれがどのように機能し、統合された3Dフィールドソルバーユーティリティを最大限に活用する方法について説明します。

インピーダンス計算:公式対フィールドソルバー

低損失ラミネート上の高データレートチャネルなど、広帯域信号を持つ高度な設計では、誘電体の分散が高速PCB設計の難しさの一因です。インピーダンス制御ルーティングに必要なトレース幅を決定するための出発点として、標準的なジオメトリのインピーダンス公式が非常に役立ちます。最も正確な方程式は共形写像で導出され、与えられたインピーダンスに対するトレース幅を抽出するために数値技術を必要とします。

これらの方程式を使用する問題点は、ブロードバンド信号のルーティングに使用する最適なトレース幅を決定することが困難になることです。インピーダンス方程式に分散を含めることができますが、その場合に抽出されるトレース幅は周波数の関数となり、目標インピーダンスからの逸脱を最小限に抑えるための最適なトレースを決定するための複雑な最適化問題を形成します。この理由から、ほとんどのPCB設計ツールは、トレース幅を計算するための代表的な周波数(通常はナイキスト周波数)を選択するように強制します。これらの他の設計ツールやオンライン計算機は、インピーダンスを計算する際に損失正接、スキン効果による損失、負荷容量を含めない場合があります。

高速信号の伝送線を設計する際に発生する他の問題、例えば銅の粗さなどを加えると、目標インピーダンスに一致する完璧なトレース幅を決定するためのより良い方法は、ブロードバンド分散、銅の粗さ、スキン効果による損失を含む統合フィールドソルバーを使用することです。インタラクティブルーターは、定義されたインピーダンス値を持つように適切な幅のトレースを配置します。

インピーダンス計算の設定

Altium Designerのインピーダンス制御ルーティングは、Simberianからの統合フィールドソルバーを使用します。これは、回路図が完成した後、しかしボードのレイアウトを始める前に開始します。PCBスタックアップを設計する際には、この機能を設定したいでしょう。空のPcbDocファイルを作成した後、「設計」メニューに移動し、「レイヤースタックマネージャー」をクリックします。スタックアップの作成を終えた後、異なるレイヤーペアのインピーダンス計算を開始できます。異なるレイヤーペアに必要なインピーダンス値を取得するには、レイヤースタックマネージャーウィンドウの下部にあるインピーダンスタブをクリックする必要があります。

インピーダンスプロファイルの作成

ここから、スタックアップ内の異なるレイヤーペアに対して、単線インピーダンスと差動インピーダンスのプロファイルを作成できます。インピーダンスプロファイルを使用すると、指定したインピーダンスを設定でき、ツールはそのインピーダンス値に設定するトレース幅を返します。差動信号の場合、差動プロファイルを作成し、差動ペア間のトレース間隔を指定すると、インピーダンスプロファイラーは必要なトレース幅を返します。また、間隔を希望する値に調整すると、インピーダンスプロファイラーは応答してトレース幅を調整します。

Altium Designerで10層PCBのインピーダンスプロファイラーツールを使用する。

単端および差動インピーダンスの組み合わせ

高速差動信号規格の下では、差動インピーダンスを特定の値に設定すると同時に、ペア内の各トレースの単端インピーダンスをそれぞれの値に設定する必要があります(Ethernetが一例です)。これを行うには、関連する信号に対して2つのインピーダンスプロファイルを作成します。1つは単端プロファイル、もう1つは差動プロファイルです。このプロセスは以下の通り進行します:

- 単端ネットのインピーダンス制御に必要な幅を決定するために、単端インピーダンスプロファイルを作成します。

- 差動インピーダンスプロファイルを作成し、希望するインピーダンスと許容値を設定します。

- 単端プロファイルから決定した幅を同じレイヤーの差動プロファイルにコピーします。

- 差動インピーダンスが希望の値に達するまで、間隔を手動で調整します。

下の画像は、差動プロファイルの差動インピーダンスと単端インピーダンスがそれぞれ85オームと50オームに一致している、このタイプのインピーダンス制御を示しています。

Altium Designerで単端および差動インピーダンス制御ルーティングプロファイルを定義する。

関連するインピーダンスプロファイルが定義されたので、これらを制御インピーダンスルーティングのための設計ルールとして有効にする時が来ました。

インピーダンス制御のための設計ルールの使用

シングルエンドネット

次に定義する設計ルールでは、必要なインピーダンスを維持するために必要な幅を指定します。設計ルールの設定を開始するには、「PCBルールと制約エディタ」を開きます。「設計」メニューをクリックし、次に「ルール」オプションをクリックします。エディタの左側のリストを見ると、「ルーティング」のエントリがあります。「ルーティング -> 幅」オプションをクリックします。下の画像では、シングルエンドインピーダンスプロファイルが有効になっています(S50と名付けられたプロファイル)。これにより、ルーターはインピーダンスプロファイルで定義された幅のトレースを配置するように強制されます。

Altium Designerでインピーダンス制御ルーティングを設定する。

このダイアログには2つの重要なポイントがあります。まず、特定の信号層または特定の信号ネットのトレースにインピーダンス制御を適用するか選択できます。ここでは、「NetR_BIAS_1」(ダイアログの上部近くで選択されたシングルエンドネット)に適用されています。二つ目に、すべてのネットに対してインピーダンスプロファイルを全層にわたる一律の設計ルールとして適用することもできます。「すべてのネット」オプションを選択することにより、また、このオプションをネットクラスに適用すると、単一のクラス内の複数のネットに自動的にルールが適用されます。

ダイアログの下部にある表では、インピーダンスプロファイルで有効になっているレイヤーを確認できます。ここでは、ルールはルーティング中にTopLayerとBottomLayerにのみ適用されます。他の信号レイヤーを有効にするには、レイヤースタックマネージャに戻ってインピーダンスタブを開きます。ここから、この設計ルールを適用したい他のレイヤーを有効にできます。

差動ペア

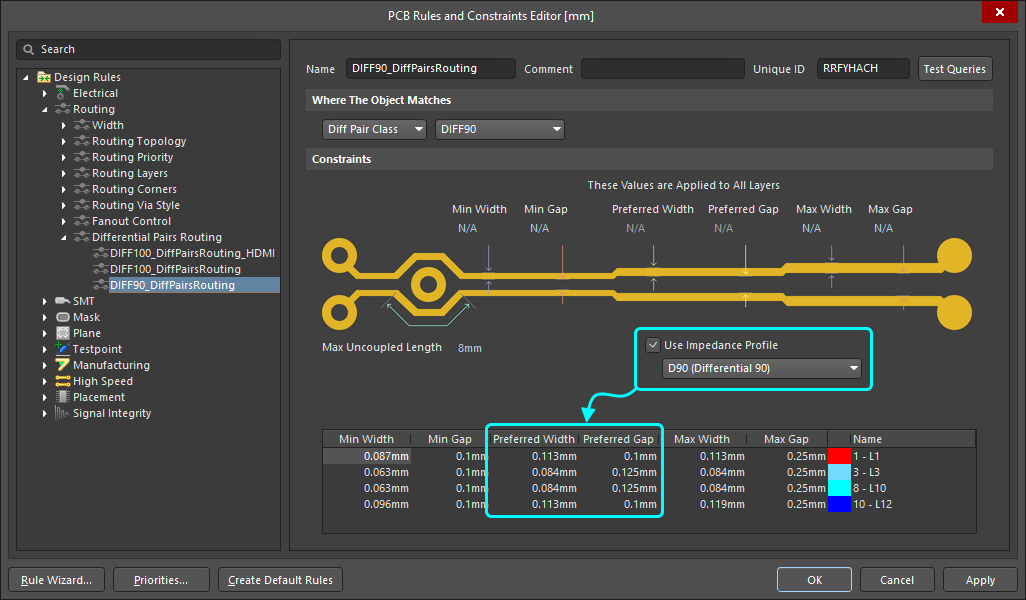

差動インピーダンスプロファイルを適用するには、PCBルールと制約エディタのRouting -> Differential Pairs Routingオプションに移動します。ここから、レイヤースタックマネージャで設定した差動インピーダンスプロファイルを有効にできます。この場合、差動ペアのインタラクティブルーターを使用するとき、ルーターはインピーダンスプロファイルで定義した必要なトレース幅と間隔を強制します。

以下に示されているのは、PCBルールと制約エディタからの画像で、差動インピーダンスプロファイルが適用され、差動ペアクラス内のすべてのペアのインピーダンスを90オームに設定しています。

特定の単線ネットやネットクラスに対して規則を適用できるのと同様に、上記のように特定の差動ペアや差動ペアクラスに対しても差動インピーダンス制御ルーティングを適用できます。この規則を適用する特定のネットやクラスを、PCBルールと制約ダイアログの上部で選択できます。また、単線ネットの場合と同様に、差動インピーダンス制御規則を適用する特定のレイヤーを有効にすることもできます。

ルーティングを開始する時間

レイヤースタックが完成し、設計ルールを通じてインピーダンス制御が有効になったので、PCBレイアウトでのルーティングを開始できます。インタラクティブルーターを使用しているときは、ルーティングすると画面の下部のステータスバーに「[Width From: Rule Preferred]」と表示されることに気づくでしょう。トレースは、事前に定義された幅(および差動ペアの場合は定義された間隔)でボード上に表示されます。

インピーダンス制御は、ルーティングする際に自動的にトレースの幅を定義します

インピーダンス制御ネット(単線および差動の両方)を使用する際、ルーティングツールは自動的に設計ルールで設定した幅を優先します。幅を手動で調整する必要はありません。しかし、異なる幅を適用したい場合は、レイヤーごとに代替の優先度制約を定義する、特定のネットに対して部屋ベースの制約を定義するなど、いくつかのオプションがあります。これにより、PCBの異なる領域で幅の制約を変更でき、インタラクティブルーターによって自動的に適用されます。

最終的に、PCB内のインピーダンス制御ルーティングは、トレースの適切な幅を決定するために信号整合性シミュレーションを実行しない限り、正確ではありません。これらの側面のいくつかはAltium Designerで調べることができますが、他のものは外部のソフトウェアアプリケーションが必要です。考慮できる重要な信号整合性メトリクスには、次のものがあります:

Altium Designerでは、インターコネクトの受信側で大きなインピーダンスの不一致を、反射波形を見ることで調べることができます。これは上述の単一ビット応答波形になります。これにより、リンギングや、HIGH論理状態の電圧閾値範囲の高/低端を超える可能性の特定が可能になります。これを正しく行うには、信号ピンのインターフェースを正確に記述する必要があり、これにはピンのロジックファミリーの知識またはIBISモデルの使用が必要です。一部のメーカーは、Altium DesignerのSignal Integrity Analysis機能などの時間領域信号整合性アナライザーでのダウンロードおよび使用のためにIBISモデルを提供しています。

Altium Designerのルール駆動型設計エンジンにより、インピーダンス制御ルーティングスキームを簡単に実装できます。既存の設計に信号整合性の問題がある場合、信号整合性シミュレーターは可能な終端スキームを反復して結果を示し、トレースを終端するための適切なスキームを選択できるようにします。

Altiumの専門家に今日相談して、Altium Designerのルーティングおよび信号整合性ツールについて詳しく学びましょう。